【应用】32Gbps PCIe PHY和控制器解决方案提供高效互连,支持2.5Gbps至32Gbps的数据速率

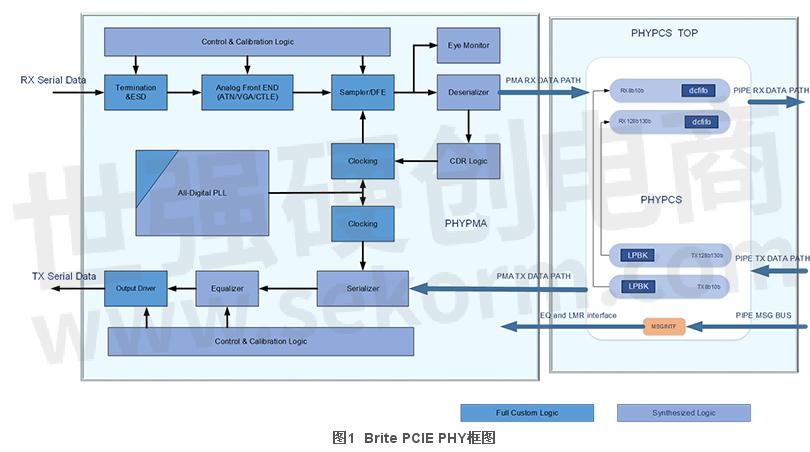

灿芯半导体32Gbps PCIe PHY和控制器解决方案提供了高效的互连,在PPA方面具有明显的优势。该系统可以支持短距离或长距离通道,以满足大量的应用场景。除了具有高线速的PHY的高性能外,低延迟也是Brite 32Gbps PCIe PHY的一个关键特征。该PHY支持2.5Gbps至32Gbps的数据速率,可以覆盖PCIe Gen5.0/4.0/3.0/2.0/1.0。 共用的LC-PLL时钟生成器可以为多达8个数据通道提供高速时钟,数据通道的数量可以进行灵活的宏观配置,例如1x、2x、4x、8x。PCIe PHY的顶层框图见图1。

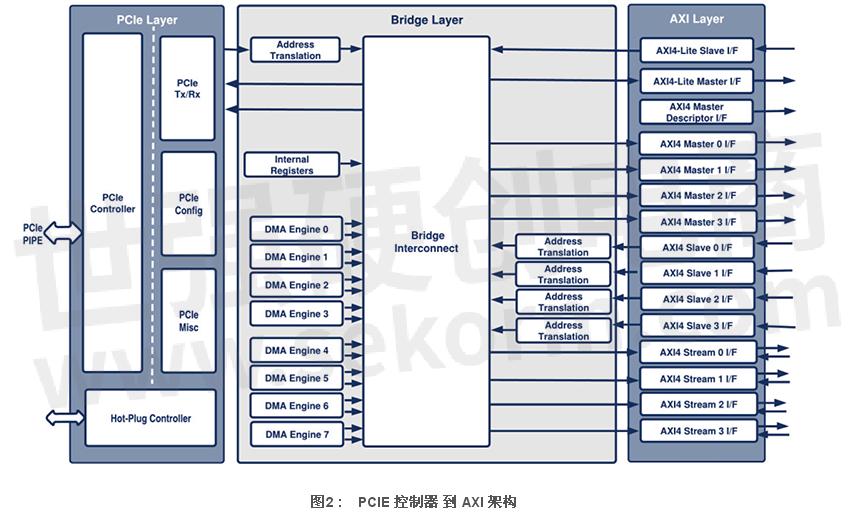

Brite PCIe控制器到AXI架构如图2所示。它在PCI Express和最新版本的AXI协议之间提供了一个高性能、易于使用的互连解决方案。它继承了领先的架构,具有内置DMA的AXI用户界面,符合AMBA® AXI3和AXI4规范。

控制器特性:

x1, x2, x4, x8, x16 PCI Express核心

支持每通道2.5、5.0、8.0、16.0和32.0 GT/s的链接速率

8位、16位、32位、64位和128位PIPE接口

符合PCI Express的PHY接口(PIPE),符合修订版4.4.1/5.2

符合PCI Express®基础规范修订版5.0 v1.0

4 KByte最大有效载荷

1个虚拟通道(VC)

支持通道反转

集成时钟域交叉(CDC),支持用户选择的桥接频率

可选的AXI4-Lite从属接口用于网桥配置

用于外部寄存器配置的可选AXI4-Lite主接口

PHY特性:

金属堆栈1P9M,待定

1.5字时钟的恒定延迟

灵活的宏配置

单个CMU最大支持x8

支持所有主要校准和自适应过程的自适应,以获得稳定的性能

支持对所有自动适应过程的软件控制和重写

支持共用参考时钟和无SSC(SRNS)的独立参考时钟

支持SSC

独立参考时钟模式的最大+/-300ppm频率偏移

用于RX性能和TX-to-RX回路性能的片上眼图监测逻辑

支持链接EQ训练的DIR模式(PIPE)

- 实现了RX眼图监控

完全符合PCIE Express Base 5.0和4.0,PCI Express Base 3.1/2.1/1.1电气规范

符合PIPE修订版4.4.1/5.2

不同的回路模式:近端串联,远端并联

- |

- +1 赞 0

- 收藏

- 评论 0

本文由顾峥峥转载自灿芯半导体,原文标题为:YouPCIe.png 系统解决方案,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关研发服务和供应服务

相关推荐

面向低功耗智能互联设备,灿芯半导体推出音频/语音DSP参考设计平台

该音频/语音DSP参考设计平台基于CEVA-TeakLite-4 DSP核开发,融合了多种传感器技术、信号处理技术和无线互联技术,旨在为手持移动设备、可穿戴设备和智能家居单芯片(SoC)设计提供原型参考,降低设计风险,加快上市时间。

【应用】灿芯半导体提供MIPI IP完整解决方案,由一系列MIPI控制器和PHY构成,用于客制化ASIC/SoC设计服务

灿芯半导体日前宣布推出可用于客制化ASIC/SoC设计服务的MIPI IP完整解决方案。该解决方案由一系列MIPI控制器和PHY构成。可以帮助系统制造商和IC公司等设计高质量的ASIC/SoC产品,同时加速上市时间。

【应用】灿芯半导体YouSip-IoT物联网平台解决方案,有助于减少处理延迟时间,降低SoC设计的功耗

YouSiP-IoT是一个全面的平台解决方案,集成了ARM Cortex Mx系列MCU和CEVA TeakLite或MM系列DSP,涉及WiFi、蓝牙/BLE接口,可与一系列不同的传感器连接。该平台可以帮助客户减少处理延迟时间,增强数据安全性,提高数据速率,并降低其SoC设计的功耗。

安全芯片设计/流片/封装

提供从安全芯片架构设计到芯片成品的整体解决方案,包括厂家的选择、工艺节点的应用、IP的提供、后端设计、封装和测试方案与逻辑等方面,工艺节点主要包含180nm/130nm/110nm/90nm/65nm/55nm/40nm/28nm/14nm/等节点。

服务提供商 - 灿芯半导体 进入

灿芯半导体运用Cadence®数字设计实现和Signoff工具,提升了4个SoC设计项目的质量并缩短了上市时间

灿芯半导体(Brite Semiconductor Corporation)运用Cadence® 数字设计实现和signoff工具,完成了4个28nm系统级芯片(SoC)的设计,相比于先前的设计工具,使其产品上市时间缩短了3周。通过使用Cadence设计工具,灿芯半导体的设计项目实现了提升20%的性能和节省10%的功耗。

灿芯半导体上线芯片设计/流片/封装服务

灿芯半导体的芯片设计、流片、封装服务已于8月上线平台,并支持IP采购和定制化服务。用户可以在平台定制14nm先进工艺的芯片、提交流片生产与对应的封测服务需求、采购灿芯自主开发的IP,包含YouPHY/YouRF/YouSiP/YouAnalog/YouIO/YouSecure/YouCrypto等七大系列,及其第三方合作伙伴的IP,有特殊需求的IP也可以进行定制。

【产品】灿芯半导体新推出xSPI/Hyperbus™/Xcella™控制器和PHY整体解决方案

日前,灿芯半导体日前宣布推出xSPI/Hyperbus™/Xcella™存储器(闪存、PSRAM、MRAM 等)的控制器和PHY解决方案,适用于客制化SoC;采用自动流量控制和反馈采样技术等创新技术来达到小面积和高速率。

灿芯半导体发布通用高性能小数分频锁相环IP及相关解决方案,支持24bits高精度小数分频

灿芯半导体(上海)股份有限公司宣布成功研发出一款通用高性能小数分频锁相环(fractional-N PLL)IP,支持24bits高精度小数分频,最高输出频率4.5Ghz,另外还支持扩频时钟(SSC)功能,可以为客户提供多功能的小数分频 PLL解决方案。

灿芯半导体多速率Serdes IP方案,具有优异性能、面积和功耗

灿芯半导体为客户提供1.25-12.5Gbps多速率SERDES IP方案。该方案平滑地集成了多SERDES通路,具有同级产品中最优的性能、面积和功耗。可编译的PHY可以支持众多主流接口。

灿芯半导体ONFI 4.2 IO及物理层IP采用全数字设计,并通过流片验证测试

定制芯片设计、生产及IP授权的高新技术企业——灿芯半导体ONFI 4.2 IO及物理层IP,该IO支持SDR/NV-DDR/NV-DDR2 1.8V, NV-DDR3 1.2V, 该物理层IP采用全数字设计,具有低功耗、面积小等特点。ONFI IP已通过流片验证,将助力客户快速实现量产。

【产品】300mA输出线性稳压器OCP1303/OCP2820 ,IQ典型耗电38uA,工作电压2.2V-5.5V

灿瑞科技推出的 0CP1303 | 0CP2820 300mA输出线性稳压器,具有简单外围,仅3个陶瓷滤波电容;宽幅工作电压,工作电压: 2.2V-5.5V;静态低功耗,1Q典型耗电38uA;高输出电流,提供高达300mA输出电流。

灿芯半导体推出由USB控制器和PHY构成的USB IP完整解决方案,助力系统制造商设计高质量的ASIC/SoC产品

2022年9月9日,一站式定制芯片及IP供应商——灿芯半导体日前宣布推出可用于ASIC/SoC的USB IP完整解决方案。该解决方案由一系列USB控制器和PHY构成,可以助力系统制造商、个人电脑原始设备制造商和IC公司等设计高质量的ASIC/SoC产品。

灿芯半导体与成都纳能、芯启源合作推出完整的USB 3.0 IP解决方案

一站式定制芯片及IP供应商灿芯半导体(上海)有限公司(以下简称“灿芯半导体”)与成都纳能、芯启源电子科技有限公司(以下简称“芯启源”)共同合作,集成USB3.0物理层设计(PHY)与控制器 (Controller)并应用于40nm和55nm的工艺技术,推出完整的USB 3.0 IP解决方案。

灿芯半导体推出USB PHY解决方案,支持高速、全速和低速数据传输速率

YouPHY-USB系列IP是灿芯半导体具有自主知识产权的先进高速USB接口IP,提供可用于片上系统(SoC)设计的USB2.0 OTG PHY IP,实现完整的混合信号和OTG连接IP方案。

登录 | 立即注册

提交评论