【经验】通过配置输出时钟来优化抖动性能的方法-使用CBPro软件进行调整,以SI5345时钟芯片为例

SILICON LABS公司提供各种高速时钟信号发生器、抖动衰减器的芯片。近年来给主要通信设备商提供了大量的时钟发生器产品。广泛用于传输网、移动回传网、接入网等设备。从实际使用的情况来看,很多用户反馈使用CBPro软件配置频率计划时都会存在串扰警告,串扰问题会带来通信质量问题,这是因为串扰直接增加时钟信号的输出jitter,也就是意味着降低输出时钟信号的相噪,可能会导致通信设备出现严重的误码。

那么,配置输出时钟来优化抖动性能的方式是什么?

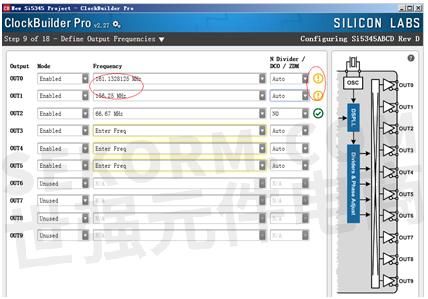

我们以Si5345时钟芯片为例。如果相邻的两个不同时钟输出的整数频率带宽接近20MHz,就可能出现串扰问题。这时候就可以使用CBPro软件进行调整。避免两个频点出现串扰,最直接的方法就是增加输出通道串扰频点的距离。图1是一个频率计划,从图上看161.1328125MHz和156.25MHz之间存在串扰。

图1:两个频点出现串扰设置

使用CBPro软件进行调整具体的操作方式如下:

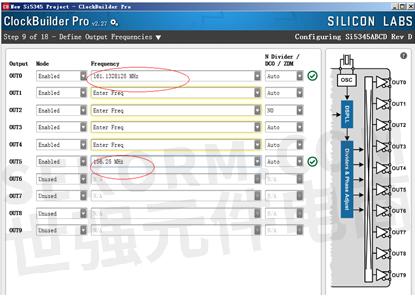

1、解决两个频点串扰问题,通过手动调整将156.25MHz选择到OUT5,来减少集成电路中的谐波串扰,如图2。

图2:避免两个频点出现串扰设置

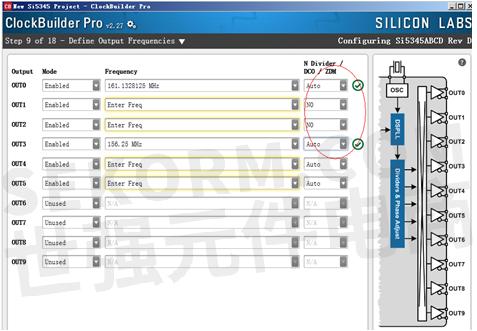

2、利用CBPro的自动设置选项,当出现两个频点串扰警告如上图1所示,点击后自动优化,输出效果完全一致,如图3所示。

图3:自动优化频点截图

3、另外选择差分输出格式。差分输出产生均衡的,互补的信号,产生较少的共模噪声,减少电磁干扰。同时还具备另一个的优点,差分输出一般功耗更低。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由飞翔提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【成功案例】SI52112双路PCIE时钟芯片在工业通信中的应用,支持PCIE1.0,2.0,3.0

在工业通信中CPU和交换芯片通常采用PCIE接口,就需要两对100M的差分时钟,我们在选取双路PCIE时钟时需要考虑稳定性,价格,货期,对比了IDT,Pericom,最后选取Silcon labs的SI52112。SI52112双路PCIE时钟芯片,支持PCIE1.0,2.0,3.0,具有低功耗HCSL差分输出缓冲器,具有很低的EMI,工业级温度,在-40~+85度下可靠运行,具有小尺寸封装。

设计经验 发布时间 : 2018-08-30

【经验】无线时钟芯片SI5386的XAXB_ERR告警问题如何解决?

SI5386是Silicon Labs公司一款经典的无线时钟芯片,日前某客户在使用SI5386时,碰到了一则XA/XB的告警问题,问题现象是使用SPI接口对SI5386做初始化后,检查输出端没有正常时钟输出。本文就将分析并解决该问题。

设计经验 发布时间 : 2021-05-11

【经验】Silicon Labs时钟芯片Si5332更改时钟输出频率的方法

Silicon Labs推出的Si5332任意频率的时钟发生器提供最高级别的集成,实现在 10/25/100G 数据中心、通信和工业应用程序中的完整时钟树整合。该芯片输出频率范围为5~ 333.33 MHz,具有 175fs 典型值的抖动性能,根据封装不同有 6路、8路、12路-时钟输出。它既可以工厂预先编程,也可以通过I2C接口,进行系统内编程。

设计经验 发布时间 : 2019-01-09

一款适合IEEE 1588V2的专用时钟芯片

Silicon Labs日前推出了专门实现IEEE 1588协议的超低抖动时钟芯片SI5348,这款芯片可以满足IEEE 1588 V2组网对系统时钟极其苛刻的指标要求,完美实现IEEE 1588 V2协议。

新产品 发布时间 : 2016-08-13

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

原厂动态 发布时间 : 2018-06-27

【经验】无线时钟芯片SI5386的free run和holdover功能应用注意事项

SI5386是Silicon Labs一款非常经典的无线时钟芯片,已经在多个基站设备(如RRU)中有大量的成熟应用。日前有工程师反馈一则holdover功能问题,记录频率数据时出现了接近200Hz的频点偏差。本文将具体分析并解决该问题。

设计经验 发布时间 : 2021-03-26

【产品】更适合IEEE 1588设计的超低抖动时钟芯片SI5388/SI5389

Silicon Labs在充分调研了各大设备商的IEEE 1588产品设备后,实时发布了另外一款支持最新IEEE 1588协议的时钟芯片SI5388/SI5389,并且在全球主流的通信设备厂家配合Xilinx、Intel等平台进行了完整的同步测试。

新产品 发布时间 : 2020-01-01

【产品】抖动率低至0.3ps的去抖时钟芯片Si5326在光模块中的应用

去抖是光模块接收中极其重要的设计之一。Silicon labs的去抖时钟芯片Si5326采用DSPLL专利技术,输出频率抖动最小可以达到0.3ps,因此常被用于光模块接收器当中用来做去抖设计。

新产品 发布时间 : 2016-12-05

【经验】去抖时钟芯片SI5347的软复位寄存器应用注意事项

SI5347是Silicon Labs公司的去抖时钟芯片,SI5347裸片上电时需要初始化,在使用中也经常进行时钟的实时调整,因此会使用到软复位以使配置生效。不过有些场合功能寄存器修改是不需要进行软复位就生效的,本文就主要分析这两种情况。

设计经验 发布时间 : 2021-03-14

【经验】如何利用CBPro软件规避时钟串扰问题?

Silicon Labs SI534X系列抖动衰减时钟,广泛用于传输网、移动回传网、接入网等设备。

设计经验 发布时间 : 2018-02-19

【经验】Silicon Labs时钟芯片Si5332写入配置寄存后无频率输出解决方法

Si5332是Silicon Labs公司推出的任意频率的时钟发生器,被广泛应用于消费电子、电信传输网、基站、数据中心等。该芯片输出频率范围为5~333.33 MHz,具有175fs典型值的抖动性能,同时该芯片具有任意频点输出、可内置多组频率计划等特点。在应用中,Si5332在写入配置寄存器后,没有频率输出,该如何解决呢?本文将详细讲解。

设计经验 发布时间 : 2019-03-13

【经验】超低相位噪声抖动衰减时钟芯片Si5382如何输出同步使能?

Si5382是Silicon Labs超低相位噪声抖动衰减时钟芯片,为每个输出端口时钟提供单独的使能OE控制bit位和外部全部输出使能控制引脚,没有可以同时控制其中几个输出使能的引脚或者寄存器。本文将具体说明如何解决同步使能。

设计经验 发布时间 : 2021-03-06

【经验】Silicon Labs时钟芯片Si5335型号定制方法

Silicon Labs 时钟发生器Si5335输出可配置多达四个输出频率,范围为1~350MHz,单一型号可以最多指定3个唯一的器件配置,因此Si5335可以代替3个独立时钟发生器或缓冲器.此外,易于使用的ClockBuilder Pro配置实用工具,使si5335成为业界最容易定制的时钟解决方案,本文将重点介绍型号定制的方法。

设计经验 发布时间 : 2019-01-21

一个使用无线专用去抖时钟芯片Si5386配置JESD204B接口时钟延时的应用案例

Silicon Labs公司的无线专用去抖时钟芯片Si5386集成DSPLL核心技术的JESD204B去抖时钟芯片,广泛用于无线基站设备中,用来消除由于离散的VCXO和环路滤波器组件带来的额外噪声。本案例就是一个实现4对延时调节功能JESD204B的DCLK/SYSREF配置的例子。

应用方案 发布时间 : 2019-04-10

【经验】高性能无线消抖时钟芯片Si5382A-E-GM失锁问题分析

Si5382A-E-GM是Silicon Labs公司推出的高性能无线消抖时钟芯片,由于大量在无线基站中使用,工程师在使用Si5382时经常反馈一些问题,本文就将分析其中一则失锁情况进行分析并解决。

设计经验 发布时间 : 2020-12-12

电子商城

现货市场

服务

提供是德(Keysight),罗德(R&S)测试测量仪器租赁服务,包括网络分析仪、无线通讯综测仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器租赁服务;租赁费用按月计算,租赁价格按仪器配置而定。

提交需求>

提供是德(Keysight)网络分析仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器维修,支持一台仪器即可维修。具备十年以上维修经验工程师,维修后测试合格率达98%,维修保修期长达三个月。

提交需求>

登录 | 立即注册

提交评论