【技术】I2C上拉电阻详细设计指南与案例分析介绍

上一篇我们针对I2C基础知识作了介绍(点击此处阅读【技术】电科星拓带你一文了解I2C基础知识及应用注意事项),本文重点对I2C上拉电阻的应用进行详细介绍与案例分析。

I2C(Inter-Integrated Circuit),中文描述为集成电路总线。它是一种串行通信总线,使用多主从架构,是由飞利浦公司在80年代初设计的,方便了主板、嵌入式系统或手机与周边设备组件之间的通讯。由于其简单性,它被广泛用于微控制器与传感器阵列、显示器、IoT设备、EEPROM等之间的通信。

I2C主要特点如下:

只需要两条总线;

没有严格的波特率要求,例如使用RS232,主设备生成总线时钟;

所有组件之间都存在简单的主/从关系,连接到总线的每个设备均可通过唯一地址进行软件寻址;

I2C是真正的多主设备总线,可提供仲裁和冲突检测;

传输速度分为四种模式:

标准模式:Standard Mode = 100Kbps

快速模式:Fast Mode = 400Kbps

高速模式:High speed mode = 3.4Mbps

超快速模式:Ultra fast mode = 5Mbps

最大主设备数:无限制;

最大从机数:理论上是127。

对I2C知识做简单回顾后,下面我们分九个部分,对I2C上拉电阻的应用做详细的讲解与案例分析。首先带大家了解下I2C总线的硬件架构。

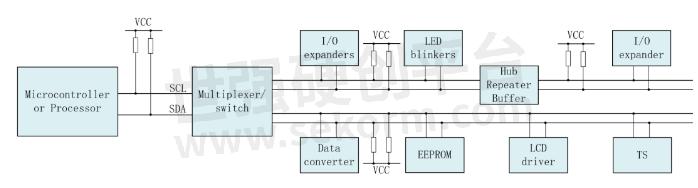

I2C总线硬件架构

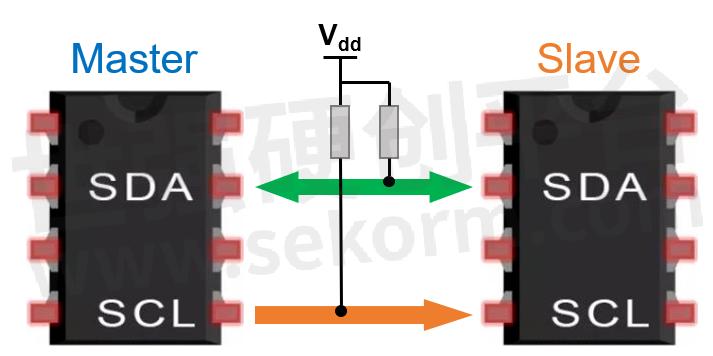

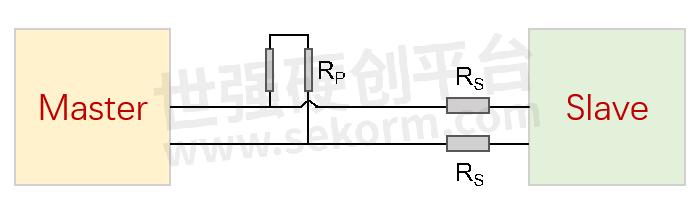

I2C协议仅需要SDA和SCL两个引脚。SDA是串行数据线的缩写,而SCL是串行时钟线的缩写。这两条数据线需要接上拉电阻。设备间的连接如下图所示:

使用I2C,可以将多个从机(Slave)连接到单个主设备(Master)(一对多通信),并且还可以有多个主设备(Master)控制一个或多个从机(Slave)(多对多通信)。

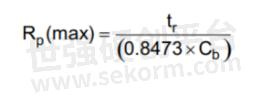

I2C总线(SDA,SCL)内部都使用漏极开路驱动器(开漏驱动),因此SDA和SCL可以被拉低为低电平,但是不能被驱动为高电平,所以每条线上都要使用一个上拉电阻,默认情况下将其保持在高电平。

I2C的上拉电阻可以是1.5K,2.2K,4.7K,电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响,一般接1.5K或2.2K。

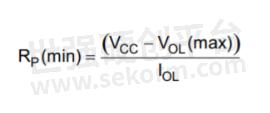

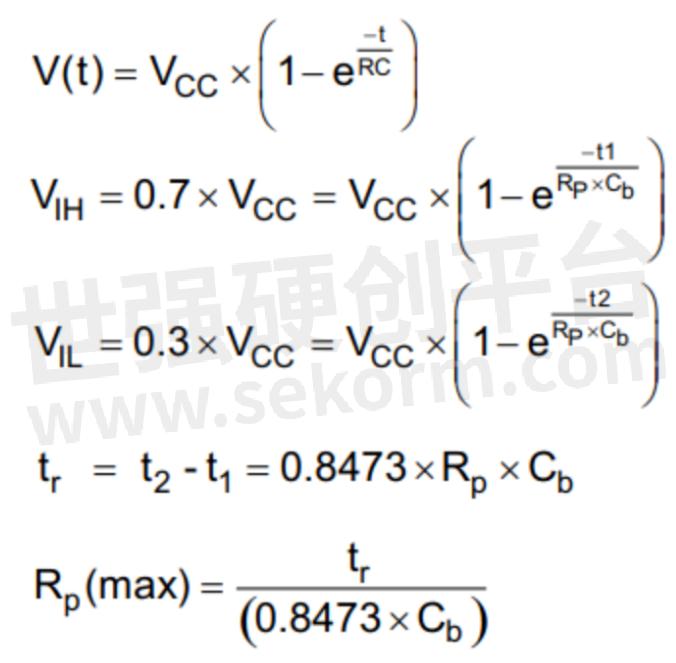

上拉电阻的值取决于许多因素,确定I2C上拉电阻可以通过下面的公式计算出来:

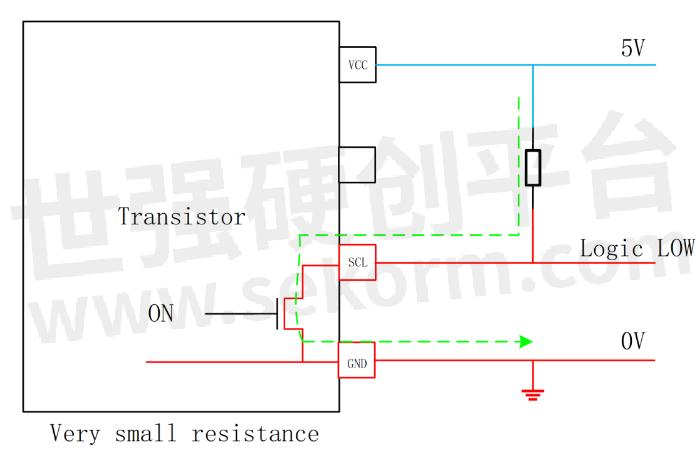

强上拉(小电阻)是用来防止芯片上的I2C引脚被驱动为低电平。可以被芯片的输入缓冲器读取为有效逻辑低电平的VOL电平决定了最小上拉电阻[RP(min)]。RP(min)由VCC、VOL和IOL组成的如下公式计算出来:

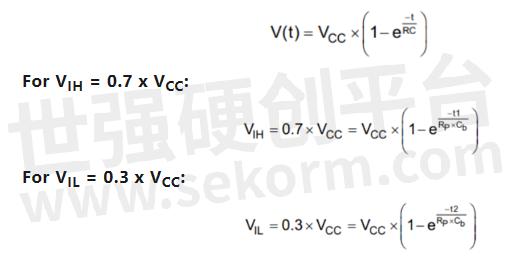

由于I2C标准定义了上升时间标准,最大上拉电阻受到总线容值(Cb)的限制。如果上拉电阻值过高,I2C总线在被拉低之前可能不会上升到逻辑高。RC电路对在时间t=0开始的幅度为VCC的电压阶跃的响应由时间常数RC表征。电压波形可以通过以下三个公式计算出来:

I2C总线的上升时间可以通过下面公式推算出来:

![]()

最大上拉电阻是一个由最大上升时间为其中最主要一个因素构成的公式,请参考以下公式:

其中:

VOL 是逻辑低电压;

IOL 是逻辑低电流;

tr 是信号的最大上升时间;

Cb 是总线电容;

具体如下表所示:

这里不难发现在做电阻选择时要满足以下几个条件:

灌电流最大值为3mA;

I2C总线规范和用户手册还为低电平输出电压设置了最大值为0.4V。

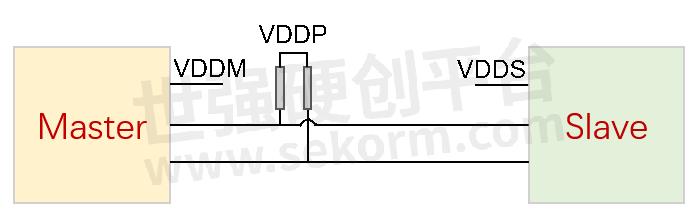

所以根据上述公式可以计算,对于5V的电源,每个上拉电阻阻值至少1.53KΩ,而对于3.3V的电源,每个电阻阻值至少967Ω。如果觉得计算电阻值比较麻烦,也可以使用典型值4.7KΩ。

最终在调试的时候,当测量SDA或SCL信号并且逻辑Low上的电压高于0.4V时,我们就可以知道灌电流太高了。如下图所示:

当然,这并不意味着每当灌电流超过3mA时,设备就会立即停止工作。但是,在操作超出其规格的设备时应始终小心,因为它可能导致通信故障,缩短其使用寿命甚至永久损坏设备。从硬件架构可以看出I2C的上拉电阻是必须的,那上拉电阻的阻值应该如何确定呢?带着这个疑问我们一起通过下面的内容寻找下答案。

I2C总线上拉电阻的阻值确认

由于I2C接口采用Open Drain机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻RP将信号线拉至高电平。因此I2C总线上的上拉电阻是必须的。

RP不宜过小,一般不低于1KΩ

一般IO端口的驱动能力在2mA~4mA量级。如果RP阻值过小,VDD灌入端口的电流将较大,这导致端口输出的低电平值增大(I2C协议规定,端口输出低电平的最高允许值为0.4V),如果灌入端口的电流过大,还可能损坏端口。故通常上拉电阻应选取不低于1KΩ的电阻(当VDD=3V时,灌入电流不超过3mA)。

RP不宜过大,一般不高于10KΩ

由于端口输出高电平是通过RP实现的,线上电平从低到高变化时,电源通过RP对线上负载电容CL充电,这需要一定的时间,即上升时间。端口信号的上升时间可近似用充电时间常数RPCL乘积表示。

信号线负载电容(对地)由多方面组成,包括器件引脚、PCB信号线、连接器等。如果信号线上挂有多个器件,负载电容也会增大。比如总线规定,对应400Kbps速率应用,信号上升时间应小于300ns,假设线上CL为20PF,可计算出对应的RP值为15KΩ。

如果RC充电时间常数过大,将使得信号上升沿变化缓慢,达不到数据传输的要求。因此一般应用中选取的都是几KΩ量级的上拉电阻,比如都选取4.7K的电阻。

小阻值的RP电阻增大了端口Sink电流,故在可能的情况下,RP取值应稍大一点,以减少耗电。另外,通常情况下,SDA,SCL两条线上的上拉电阻取值是一致的,并上拉到同一电源上。

由于信号线负载电容对设计会产生较大影响,我们单独用一节来介绍下I2C总线寄生电容的具体组成与注意事项。

I2C总线寄生电容

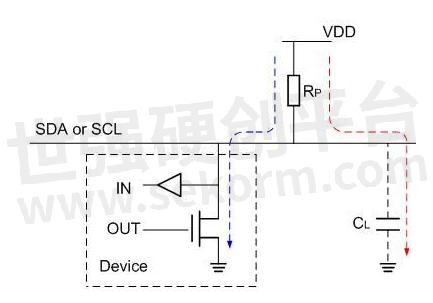

I2C总线寄生电容主要有master寄生电容、slave寄生电容和PCB走线电容组成,如下图所示:

这些寄生电容共同组成I2C总线的电容,I2C主机和从机越多,I2C总线上的电容就越大。根据相关文档,不同的I2C通信模式对寄生电容的要求不同,具体如下表所示:

正是因为这个寄生电容的存在,导致I2C总线上拉电阻的选择会受到限制。另外在一些特殊应用中还需要保证I2C较强的抗干扰能力,下面我们就来看下如何通过设计来实现较强抗干扰能力。

I2C总线布线与抗干扰设计

I2C信号线属于低速控制线,在手机PCB设计时,按通常的控制IO对待即可,无需做特别的保护设计,一般不用担心受到噪声源干扰。

但在一些特定的情况下,比如折叠、滑盖机型中,I2C的两根信号线需要通过转轴或滑轨处的FPC,此时由于信号路径比较长,距离天线比较近,而且Open Drain的输出级对地阻抗大,对干扰比较敏感,因此比较容易受到RF信号源的干扰。在这种情况下,就应适当注意对I2C信号线的保护。比如I2C两条信号线(SDA,SCL)等长度地平行走线,两边加地线进行保护,避免临近层出现高速信号线等。

上拉电阻应安置在OD输出端附近。当I2C总线上主从器件(Master & Slave)两端均为OD输出时,电阻放置在信号路径的中间位置。当主设备端是软件模拟时序,而从设备是OD输出时,应将电阻安置在靠近从设备的位置。

I2C协议还定义了串联在SDA、SCL线上电阻Rs。该电阻的作用是有效抑制总线上的干扰脉冲进入从设备,提高可靠性。这个电阻的选择一般在100~200Ω左右。当然,这个电阻并不是必须的,在恶劣噪声环境中,可以选用。

比如常用的FM接收模块或者Capsense触摸感应功能块,都是通过I2C接口控制的。I2C接口信号从处理器出发,经过PCB上的信号路径,进入上述电路单元。I2C信号线上载有一定干扰,这种干扰虽然幅度并不很大,但还是会影响敏感的FM接收模块或Capsense触摸感应功能块。此时,可以通过在靠近FM模块或触摸感应模块的I2C信号线上串接Rs电阻,即可有效降低干扰的影响。此外,上拉电阻端的电源也要进行退耦处理。

上拉电阻的阻值大小会影响上升沿爬升时间,从而影响I2C的通信频率,下面我们来具体看下会产生哪些具体影响。

I2C总线上拉电阻对通信频率的影响

I2C总线通信,无非就是传递高低电平,针对于高电平或者低电平变化,那么需要分别分析上拉电阻的影响。

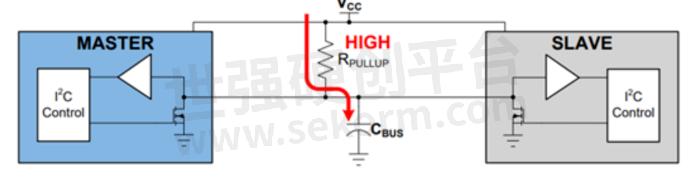

1、I2C总线电平由低到高时

如下图所示:

由于I2C器件的硬件结构为Open Drain,所以当I2C总线电平由低到高时,I2C器件(同一时刻,可以是I2C主机,也可以是I2C从机)释放总线电平,即内部的MOSFET关闭,如此,Vcc经过上拉电阻对I2C总线寄生电容充电,直至到达Vcc。时间常数即为RC网络。

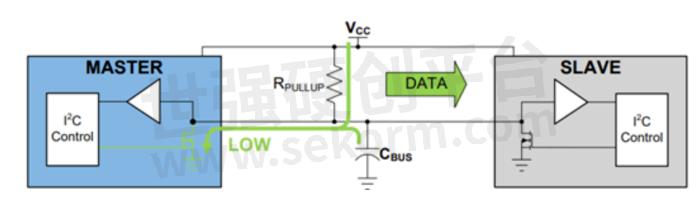

2、I2C总线电平由高到低时

如下图所示:

当I2C总线电平由高到低时,I2C器件(同一时刻,可以是I2C主机,也可以是I2C从机)拉低I2C总线,MOSFET导通,所以I2C总线的寄生电容通过MOSFET的导通电阻放电,由于导通电阻往往很小,所以放电速度很快。

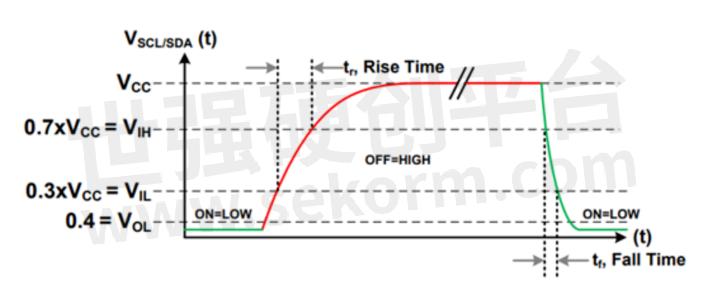

3、I2C总线的上升下降时间对比

如下图所示,为I2C总线上升沿和下降沿的曲线,可以看出上升时间远远大于下降时间,也就是说I2C总线的通信频率受上升时间影响最大,进一步,I2C总线上拉电阻影响I2C的通信频率,即上拉电阻阻值越大,就越限制I2C的通信频率。

另外,根据电容的充放电公式,可以得出以下公式,确定I2C总线上拉电阻的最大值。

因此,根据给定的I2C通信模式,可以确定I2C总线上拉电阻阻值的最大值。下面我们就来看下如何确定最小值呢?

I2C总线上拉电阻对VOL的影响

如下图所示,在I2C主机发出低电平时,内部的MOSFET导通,导通电阻Rdson与I2C总线上拉电阻Rpullup组成电阻网络。根据戴维南定理,如果上拉电阻Rpullup阻值越小,则Rdson上的电压VOL就越大。显然,如果VOL大于某一特定值,I2C从机就无法监测出I2C总线上的低电平。另外,如果上拉电阻Rpullup阻值过小,系统功耗也会增加。

所以,通过这个分析可以确定I2C总线上拉电阻的最小值。

以上我们讲的是硬件实现的I2C总线方式,现实中还会存在软件实现I2C的应用,下面我们就来看下在软件I2C实现中上拉电阻如何应用。

I2C总线软件模拟中上拉电阻的应用

由于一般的I2C应用速率并不高(400Kbps),使用处理器的IO口模拟I2C波形,完全可以胜任(处理器一般担任Master,占有I2C通信的控制权,无需担心随机的I2C通信服务中断其他任务的执行)。

处理器分配给I2C任务的IO口,要求可以输出高低电平,还能配置为输入端口。处理器根据总线规范以及从设备的时序要求,利用2条IO信号线,模拟I2C接口时序波形,进行I2C通信。

处理器发送数据时,通过IO口输出高电平,上升时间基本与外部上拉电阻阻值无关,且比用外部上拉电阻上拉到高电平快很多。处理器在接受数据时,即便上拉电阻阻值选的大一些,从设备输出数据的波形上升沿缓慢,但由于处理器使用软件采样的而非硬件采样,因此,对数据传输的结果并不影响。也就是说,使用IO口模拟I2C时序时,上拉电阻阻值可以适当选的大一些。

需要指出的是,使用软件模拟最多只能完成单Master的应用,对于多Master应用,由于需要进行总线控制权的仲裁管理,使用软件模拟的方法很难完成。

I2C总线空闲的时候,两条信号线应该维持高电平。否则,上拉电阻上会有耗电。特别是在上电过程中,IO线上电平也应保持在高电平状态。也就是说:当Master的I2C使用的是IO软件模拟时,一定要保证该两个IO上电默认均为输入(或高阻)或者输出高电平,切不可默认为输出低电平。IO默认为输入时,可以通过外部上拉电阻将I2C信号线拉至高电平。

在I2C实际应用中还会遇到类似电源倒灌的问题,它会影响I2C的通信可靠性,严重的会影响到芯片工作,下面我们就来重点看下如何规避此类问题。

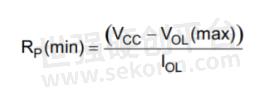

I2C总线应用中上拉电阻电源问题

在部分应用中,还存在主从设备以及上拉电阻电源不一致的情况,比如Camera模组。在很多设计方案中,Camera模组不工作时,并不是进入Power Down模式,而是直接关闭模组供电VDDS。此时,处理器与模组相互连接的所有信号线都应该进入高阻态,否则就会有电流漏入模组,而对于此时的I2C控制信号线来说,由于上拉电阻的存在,必须关断上拉电阻电源VDDP。如果上拉电阻使用的是系统电源VDDM(VDDP=VDDM),无法关闭,就会有漏电流进入模组,因此这种情况下,应该使用VDDS作为上拉电阻电源(VDDP=VDDS),这样上拉电阻电源与Slave电源即可同时关闭,切断了漏电路径。

另外需要注意的是,在上述应用实例中选择的IO,应该选取上电默认为输入(或高阻)才行。

根据上述几节的分析,可以很简单的计算出I2C总线上拉电阻的阻值范围。下面我们通过一个实际案例来回顾下上述内容。

I2C总线上拉电阻阻值计算实例

例如,在I2C Fast mode下,I2C总线电容Cb = 200pF,总线电压为Vcc = 3.3V,计算上拉电阻阻值。

因此,可以得到I2C总线上拉电阻的范围,结合系统功耗和通信速度,最终确定上拉电阻的阻值。另外,某些情况下的计算会出现RP(min)大于RP(max)的情况,这个时候就需要考虑降低I2C总线电容,解决办法就是增加I2C总线中继器(Hub,Repeater,Buffer)。

综上所述

I2C碰到的各种问题,多半是上拉电阻或者控制器时钟的问题。没上拉电阻或者上拉电阻过大,都会导致不稳定而出现寻址不到的问题。

本质上来讲,I2C总线电容决定上拉电阻的最大值,I2C器件open-drain接口导通电阻决定上拉电阻的最小值。

I2C的上拉电阻选择对于所有设计I2C接口的芯片来说很重要!

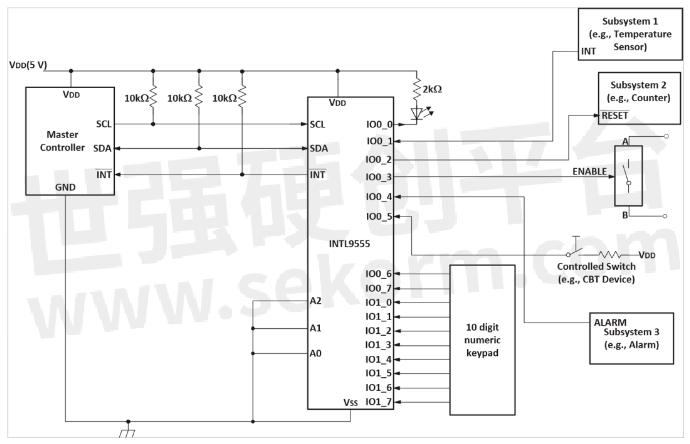

例如我们电科星拓已量产的I2C接口芯片INTL95XX与INTL96XX系列,以及留有I2C接口访问芯片内部寄存器的芯片,都很注重这个问题。一旦在实际应用中遇到类似的问题,要从本质上考虑解决这些问题。下面通过我们INTL9555(16路I2C和SMBus GPIO扩展器)的应用框图简单看下:

电科星拓I2C接口芯片系列

- |

- +1 赞 0

- 收藏

- 评论 1

本文由ll转载自电科星拓公众号,原文标题为:I2C上拉电阻应用解析,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【技术】电科星拓带你一文了解I2C基础知识及应用注意事项

23年3月电科星拓发布了I2C接口的全系列产品,对产品的功能做了简单介绍。本文关于I2C的基础知识部分进行介绍。

【技术】电科星拓带您认识时钟发生器和缓冲器

本文中电科星拓尝试给大家梳理时钟的起源和发展史,并带大家认识时钟发生器和缓冲器,以及电科星拓的时钟产品介绍,希望能解除大家心中疑惑。

25%的IoT设备无法连接到网络,是为什么?

物联网即物物相连,无线物联网技术包括蓝牙、Zigbee、wifi等技术,这些作为市面上成熟的无线通信技术,在各行各业已被广泛使用。据统计,物联网产品Wi-Fi调配失败的客户投诉率高达25%,本文讲述了可能产生的原因。

【IC】电科星拓推出I²C电平转换芯片INTL9617,工作温度-40℃~85℃,采用MSOP8封装

INTL9617是电科星拓自主研发的一款用于I2C总线和SMBus系统的双路双向电平转换芯片。该芯片可在I²C总线或SMBus应用之间提供低电压(低至0.8V)和高电压(2.2V至5.5V)的双向电压水平转换(上行转换模式和下行转换模式),使得低电压和高电压设备能够在同一个I²C总线或SMBus系统上稳定工作。

电科星拓芯片选型表

电科星拓提供以下技术参数的芯片选型表,包含:时钟Buffer芯片、时钟发生器芯片、I2C接口芯片、数字温度传感器芯片、PCIe Bridge(转SATA)芯片、DDR5 RCD芯片、DDR5 SPD Hub芯片、CDR芯片、电源管理芯片

|

产品型号

|

品类

|

系列

|

规格

|

状态

|

封装

|

|

TBUF0320

|

时钟Buffer芯片

|

TBUF系列

|

20路DB2000QL CLK Buffer (LPHCSL)

|

MP

|

LGA80

|

选型表 - 电科星拓 立即选型

【IC】电科星拓推出I²C双向转换开关芯片INTL9548/46/45,支持0至400kHz总线频率

INTL9548/9546/9545是带复位功能的8通道/4通道I²C和SMBus转换开关,INTL9545同时支持中断功能,支持低电平有效复位(RESET)输入,将RESET下拉为低电平会使I²C状态机复位,并且使所有通道取消选中,这一功能与内部上电复位功能的作用一样。

【IC】电科星拓I2C热插拔缓冲芯片INTL9511,支持I2C总线标准模式和快速模式双向数据传输

INTL9511是一款I2C总线热插拔缓冲器,支持将I/O卡插入带电背板中,而不会损坏数据和破坏时钟线路。目前,电科星拓已量产了多款I2C接口系列芯片,实现了电平转换、GPIO扩展、双向转换开关和热插拔缓冲的四大功能全覆盖。电科星拓的I2C接口系列芯片凭借其卓越的性能、可靠的品质,已经被广泛应用在服务器、存储阵列、交换机和工业设备中,实现平稳可靠的数据传输。

芯伯乐(XBLW)半导体器件选型指南

芯伯乐产品专注于消费类和工业类市场。主要产品有电源管理IC、低功耗LDO、三端稳压、高中低压MOS管、马达驱动、接口RS485/RS232、达林顿及逻辑电路等。产品广泛应用于无人机、机器人、电源、计算机、仪器仪表、玩具、家电、通讯设备、照明应用、汽车电子、工业自动化设备等领域。

芯伯乐 - 7通道达林顿晶体管阵列,三态缓冲器,8路总线收发器,DC-DC开关电源,低失调运算放大器,八位CMOS移位寄存器,八位上升沿触发D型触发器,单稳态触发器,存储芯片,八位型锁存器,JFET低功耗双运放,串行实时时钟芯片,八D型边沿触发器,低功耗运算放大器,I2C串行实时时钟芯片,三路二选一模拟开关,达林顿电路,单稳态多谐振荡器,温度传感器,音频功率放器,四路二输入或与非门电路,可调整电压,三端稳压器,电流型脉宽调制器,可编程定时器,8通道达林顿晶体管阵列,RS485收发器,逻辑电路,立体声音频功率放大器,八D型上升沿触发器,EEPROM 存储器,二输入与门集成电路,三端稳压路,双路全桥式驱动,四路R/S闩锁,多路转换器,双路全桥驱动,四路比较器,高中低压MOS管,十进制同步计数器,二上升沿触发D类触发器,音频放大器,可编程分辨率单总线温度传感器,接口芯片,AC-DC开关电源,DISCRETE DEVICE,八位并入串出移位寄存器,六路反相缓冲器和变换器,脉宽调制控制器,二路JK触发器,CMOS四路双向开关,RS485 收发器,双路D型触发器,实时时钟/日历芯片,接口RS232电路,时钟,全桥式电机驱动,通用运算放大器,IR-CUT控制电路,电源管理LC,RS485-RS422收发器,三端稳压,4路缓冲器/线驱动器,模拟开关,双十进制同步计数器,二进制分频器/振荡器,线性稳压路,逻辑器件,双路精密计时器,八位移位寄存器,八位反相缓冲器/驱动器,八缓冲器/驱动器,六路反相施密特触发器,存储器,低压RAIL TO RAIL CMOS四运放,POWER MANAGEMENT LC,三端稳压MOS管,双极性集成电路,电源管理IC,TRC,二进制串行计数器,低功耗LDO,RS485/RS422收发电路,非门集成电路,驱动电路,DRIVE CIRCUIT,计时器,四位二进制同步计数器,低压RAIL TO RAIL CMOS单运放,八D型透明锁存器,双路比较器,高性能低噪声双运算放大器,BCD转7段锁存器/触码器/驱动器,8路缓冲器/线路驱动器,四通道二输入与非门电路,DC-DC开关控制器,JFET低功耗单运放,六路反相器,CMOS通用时基定器,LOGIC DEVICE,单路运算放大器,接口RS485电路,交路反相器,全双工RS-485/RS-485/RS2-22 10MBS 收发器,实时时钟,三线-八线译码器/多路分配器,JFET低功耗四运放,双四通道模拟多路复用器/解复用器,人体红外线感应信号处理器,混合集成电路,比较器,达林顿管驱动,电源极性反转变换器,八位可寻址锁存器,AUDIO AMPLIFIER,马达驱动,脉冲宽度调制解调器,高性能模拟集成电路,七段译码/驱动器,LDO,直流马达驱动,真相与和解委员会,双精密单稳态多谐振荡器,译码计数器,可挂靠多收发器,6通道达林顿晶体管阵列,二路四选一模拟开关,双路运算放大器,开关型降压稳压器,双路二线路至四线路解码器,运算放大器,4路二输入非门电路,3通道达林顿晶体管阵列,分立器件,MOS管,ESD保护半双工RS-485/RS-422收发器,四位二进制同步加/减计数器,线性稳压器,LNTERFACE CHIP,DC-DC转换器控制电路,EEPROM存储器,三双通道模拟多路复用器/解复用器,UC2843,DS1302,UC2842,CP2139,TEA2025,UC2845,UC2844,DS1307,CD4069,74HC20,CD4073,CD4072,NE556,TL494,NE555,CD4077,24C128,CD4071,KA7500,CD4070,LM317,LM324B,74HC32,74系列,74HC595,50N06D,CD4066,74HC238,24C256,CD4060,74HC00,LM1875,74HC02,74HC04,74HC07,CP2119,CD4094,CD4518B,CD4093,SN65LBC184,74HC11,74HC14,MAX3485E,24C64,CD4511,74HC10,74HC573,74HC574,MAX3082E,74LVC00,74HC4053,74HC08,74HC4051,74HC4052,CD4082,CD4081,74XX,LMV321,CD4543,MAX3085E,LM239,LM358,CD4538,CD4541,LMV324,24C32,L7805,74HC151,74HC273,74HC153,LM321,LM324,MC33063,24C08,MAX202,74HC123,74HC244,74HC245,74HC126,24C02,24C01,24C04,DS18B20,SN75LBC184,74HC240,LM337,L78MXXH,SN65176,LM339,AMS1117,74HC132,74HC374,50P06D,74HC138,74HC259,74HC139,24C16,74HC373,L293D,CD40106,MAX3490E,ICL7660,LMV358,TDA2822,74XX系列,MAX3491E,TDA2030,74HC192,74HC193,MAX3088E,LM393,MAX481,MAX483,MAX485,MAX487,TLC555,74HC86,74HC165,TL071,MAX489,TL072,MAX488,TDA2003,ULN2001,ULN2002,CD4013,CD4012,CD4011,TL074,MAX3232,74HC160,74HC161,ULN2003,CP116,ULN2004,CP118,74HC164,4000,LM139,ULN2803,CP6208,ULN2804,LM2575,LM258,LM2576,SN75176,MAX232,MC34063,TL082,TL081,CD4001,TL084,24C512,4000系列,LM741,BISSS0001,74LVC1G14,LM2904,CD4027,CD4025,LM2901,LM2903,93C46,74HC540,74HC541,PCF8563,74HCT14,CD4528B,LM2596,MAX490,CD4017,MAX491,74HC74,L298N,CD4020,TL061,TL064,TL062,CD4021,CD4049,NE5532,CD4053,CD4052,93C66,CD4051,CD4050,SG3526,SG3524,L9110S,SG3525,UC3845,UC3846,CP1511,74LVC1G04,OP07C,UC3842,UC3843,UC3844,LM358B,74LVC1G08,TDA2050,93C56,CD4040,74HC533,74HC534,CD4043,LM293,通讯设备,工业自动化设备,机器人,INSTRUMENTATION,汽车制造,照明应用,仪器仪表,AUTOMOBILE MAKING,MEDICAL EQUIPMENT,INTERNET OF THINGS,物联网,医疗器械,玩具,数码电子,NEW ENERGY,医疗设备,无人机,DIGITAL ELECTRONICS,消费类市场,新能源,家电,仪表,电源,工业类市场,数字电子学,汽车电子,计算机

电科星拓具有中断输出的16路/8路I2C GPIO扩展芯片INTL9555/INTL9554

电科星拓INTL9555/9554是具有中断输出的16路/8路I2C和SMBus GPIO扩展器。可为两线双向I2C总线(或SMBus)提供16位/8位通用并行输入和输出扩展,该器件的工作电源电压范围为1.65V至5.5V。器件功能包括当输入端口状态发生变化时,在INT引脚上生成中断。硬件可选地址引脚A0、A1和A2,最多允许8个该器件位于同一I2C总线上。

成都电科星拓科技有限公司产品介绍

成都电科星拓科技有限公司专注于互联芯片的研发和销售,拥有多个研发中心,产品涵盖时钟、接口、高速接口和电源管理芯片等。公司通过三标管理体系认证,具备完善的E2E量产交付平台,拥有多项专利和荣誉。产品系列包括时钟芯片、通用接口芯片、高速接口芯片和电源管理芯片,广泛应用于服务器、存储、通信等领域。

电科星拓 - PCIE BRIDGE(转USB)芯片,DDR5 SPD HUB芯片,数字温度传感器芯片,I3C电平转换芯片,DDR5 RCD芯片,寄存时钟驱动器芯片,CDR芯片,I3C/SPI电平转换芯片,I2C接口芯片,PCIE BRIDGE(转SATA)芯片,时钟BUFFER芯片,时钟芯片,电源管理芯片,高速接口芯片,时钟发生器芯片,I2C电平转换芯片,通用接口芯片,DDR5 SPD芯片,XSAT系列,PEFS1215,TGEN6308,INTL9548,INTL9306,TGEN6309,INTL9544,INTL9545,XUSB系列,INTL9546,INTL系列,OCDR2822,TBUF系列,OCDR281X,STMP112,STMP431,STMP432,TBUF1308,PSTD0601,PSTD1612,TGEN6310,XSAT2102A,TBUF0210,INTL9617,XSAT2204,XSAT2202,XUSB,OCDR2814,OCDR2811,PSTD1606,RCD,OCDR280X,TBUF0208,STMP系列,TGEN系列,XUSB2102,TBUF0320,INTL3306,TGEN6302,XUSB2104,TGEN6304,MSPD系列,MSPD,TBUF0204,STMP75,OCDR,XSAT,INTL9641,OCDR2801,PEFS0505,PMIC5001,PMIC5002,PMIC5003,OCDR2804,TBUF,INTL3416,PSTD1630,XSAT2104A,RCD系列,XSAT2104,STMP,INTL9554,INTL9555,INTL9511,RCD5001,MSPD5118,TGEN6310B,PEFS1205,TBUF0308,STMP464,OCDR系列,TBUF0306,STMP5111,TGEN6320,INTL3524,TBUF1510,PSTD1620,PEFS1250,RCD5002,TGEN,RCD5003,TBUF0304,INTL3528,INTL,DDR5 RDIMM,DDR5 内存条,光纤网络交换机,个人计算机,交换机,基站,存储阵列,AUX电源,总线扩展,通信,HBA卡,热插拔缓冲,数字电视,硬件加速卡,工业PC,工业,DDR5 UDIMM,光纤收发器,光模块,路由器,GPIO扩展,医疗设备,PC DDR5内存模组,光纤网络路由器,板载光引擎,以太网卡,通信设备,DDR5 LRDIMM,电平转换,DDR5 SODIMM,AOC光缆,PCLE卡,PC,固态硬盘,光纤网卡,服务器,PON拉远,工业设备,辅助电源,计算机

INTL9546产品简介

该资料介绍了INTL9546四通道双向转换开关,它通过I2C总线控制。具有低摆率开关、支持电压级别转换(1.8V至5V)、热插拔功能等特点。适用于服务器、路由器、工厂自动化等领域。

电科星拓 - QUAD BIDIRECTIONAL TRANSLATING SWITCH,四路双向转换开关,INTL9546,FACTORY AUTOMATION,ROUTERS,路由器,工厂自动化,服务器,电信交换设备,SERVERS,TELECOM SWITCHING EQUIPMENT

电科星拓(Silicon Innovation)时钟芯片/数字隔离芯片选型指南

时钟芯片 单端缓冲器 差分缓冲器 数字隔离芯片 I2C电平转换器 I2C GPI0扩展器 I2C双向转换开关 I2C热插拔缓冲器

电科星拓 - 数字隔离芯片,I2C 热插拔缓冲器,I2C 双向转换开关,差分缓冲器,I2C GPI0扩展器,时钟芯片,I2C 电平转换器,I2C GPIO 扩展器,I2C热插拔缓冲器,I2C双向转换开关,单端缓冲器,I2C电平转换器,INTL9548,INTL9554,INTL9555,INTL9511,INTL9545,INTL9546,TBUF0308,TBUF0306,TBUF0208,TBUF1510,TBUF0210,TBUF0320,TBUF0304,INTL9617,TBUF0204

INTL9545产品简介

该资料介绍了INTL9545四通道双向转换开关的功能和应用。它支持I2C总线控制,具有四个中断输入和一个中断输出,适用于IT基础设施、汽车电子和工厂自动化等领域。

电科星拓 - QUAD BIDIRECTIONAL TRANSLATING SWITCH,四路双向转换开关,INTL9545,STORAGES,FACTORY AUTOMATION,储藏室,SERVERS,5G通信,IT基础设施,5G COMMUNICATION,IT INFRASTRUCTURE,工厂自动化,AUTOMOTIVE ELECTRONICS,服务器,汽车电子

电科星拓(Silicon Innovation)时钟缓冲器/低速接口/电源管理产品选型指南

电科星拓 - 时钟缓冲器,I2C GPIO扩展器,EFUSE,电熔丝,I2C双向转换开关,I2C电平转换器,INTL9548,INTL9554,INTL9555,INTL9545,INTL9546,PEFS0505,PEFS1205,TBUF0308,PSTD1606,TBUF0306,TBUF0208,PSTD1612,TBUF1510,PSTD1620,TBUF0210,TBUF0304,INTL9617,TBUF0204

电子商城

服务

整体外形尺寸小至0.6*0.3*0.3mm (DFN0603),工作电压范围覆盖2.5V~36V,电容值低至0.2pF,浪涌能力最高可达240安培,静电等级可达空气放电、接触放电±30KV。提供免费浪涌测试仪、静电测试仪测试。

提交需求>

可定制波导隔离器频率覆盖5.5GHz~110GHz,插损损低至0.25dB、隔离度、正向方向功率、封装尺寸参数。

最小起订量: 1pcs 提交需求>

登录 | 立即注册

提交评论