【应用】Silicon Labs符合AEC-Q100标准、适用于ADAS系统和自主驾驶硬件平台的时序解决方案

高级驾驶辅助系统(ADAS)向驾驶员提供反馈,或协助驾驶员进行驾驶操作、制动或加速,以提高车辆内外人员的安全性。ADAS系统包含复杂程度不同的各种功能,并且正在为完全自主车辆铺平道路。汽车工程师协会将自动驾驶定义了6个级别,范围从无自动化(级别0)到完全自动化(级别5)。

每个自动化级别都为车辆规定了更高程度的自主驾驶功能,这就需要更高程度的处理能力和数据路径连接性,以使用车辆内外传感器收集的数据来导航车辆。随着车辆由人控制转变为汽车自主控制,安全性变得愈发重要,并且成为ADAS系统设计中最为关键的要素之一。

ADAS系统涵盖各种应用和设计复杂性。时序要求也会有很大差异,并且随着上述的每种自动化级别逐级递进而变得越来越重要。从级别2跳至级别3需要大幅增加设计复杂性,因此为时钟树设计带来了新的挑战。采用高带宽FPGA或处理器、高速数据总线和1GbE/10GbE以太网连接带来了对混合变化频率的差分和单端时钟的需求,其中一些时钟要求抖动性能低于500fs RMS,以满足高速SerDes和PCIe-Express接口的需求。在为ADAS设计选择时序解决方案时,建议考虑以下方面:

1、总结时钟树:首先梳理所有参考时钟、性能水平以及设计中所需的相关时序功能。这通常称为时钟树。每种单独设计都有其独特的时钟树,但通常需要具有不同等级抖动性能要求的单端时钟和差分时钟。开始确定时序解决方案时对时钟树进行总结将非常有用。

2、可靠性:石英晶体和振荡器组件都是易受冲击和发生振动故障的机械设备。甚至连符合AEC-Q200标准的设备都具有较高FIT失效率,且通常是系统设计中失效率最高的组件。级别3/4/5的ADAS设计通常需要8个或更多参考时钟。在系统设计中添加越来越多的石英晶体和振荡器组件不仅会增加物料表和系统总成本,还会增加可靠性方面的顾虑,因为石英元件易受冲击和发生振动故障。一种更好的方法是将石英晶体和振荡器组件的功能集成到一个时钟发生器解决方案中,采取这种方法会大大降低与设计时序部分相关的FIT失效率,同时还会提供有益于时钟树设计的许多其他功能,例如减少EMI/EMC的扩频功能、频率选择和故障监控。

3、频率灵活性:高带宽FPGA和处理器平台需要在不同输出电压下采用单端和差分输出格式级别的变化频率的参考时钟,且所有参考时钟要求低抖动。SILICON LABS(芯科科技)获得专利的MultiSynth输出分频技术在高达12输出的整数和分数相关输出频率上均可提供0ppm合成错误,同时保持业界最佳的抖动性能。每种时钟输出都可以单独设置为特定的输出格式级别,并且可以连结不同的输出电压水平,从而轻松满足用户的系统设计要求。

4、安全合规性:在ADAS设计或模块设计中符合ISO26262标准和汽车安全完整性等级(ASIL)非常重要。在这些应用中,可能需要参考时钟冗余或健康监测来达到系统级安全目标。Silicon Labs符合AEC-Q100标准的Si5332时钟发生器包含石英晶体或振荡器解决方案无法提供的故障监控和检测功能,例如针对冗余的主参考输入和备份参考输入、输入参考健康状况和状态监测、参考信号损耗故障检测指示器、用于与ASIL系统安全管理器IC通信的硬件接口引脚以及从主输入源迁移至二次输入源的能力。

5、EMI/EMC:大多数ADAS时钟树由单端和差分参考时钟组成。单端LVCMOS参考时钟是高速数字设计中的常见发射源,并且通常是能否满足CISPR25 Class-4和Class-5发射要求的关键所在。Silicon Labs提供了一种克服这一挑战的独特方式,即在AEC-Q100 Si5332时钟发生器中使用互补性LVCMOS输出驱动器。系统设计者可以通过遵循AN1237中建议的设计指南,减少LVCMOS时钟产生的发射。

6、功能集和集成:除了以上提到的安全功能和互补性LVCMOS功能外,Silicon Labs的Si5332时钟发生器还配备了许多可以简化设计的其他功能,例如减少EMI的扩频功能、频率选择功能、硬件输出使能控制以及多配置文件选择。实现低抖动性能始终是优先考虑的事项,因此Silicon Labs的时钟发生器在所有电源引脚上都包含了片上LDO,从而带来了业界最佳的PSNR性能。通过片上实现抑制外部电源和板级噪声极大减少了电源滤波所需的外部组件数量,从而降低了电路板空间和成本,并确保了输出时钟抖动性能符合数据表规格限值。

7、PCIe时序:PCI-Express是一种用于级别3/4/5 ADAS设计的常用数据总线,这增加了每个PCIe端点对低抖动差分参考时钟的需求。Silicon Labs的Si5332可编程时钟发生器、Si5225x PCIe Gen1/2/3/4/5时钟发生器和Si5325x PCIe Gen1/2/3/4/5具有带内部端接的低功耗HCSL输出驱动器,能够匹配85ohm或100ohm传输线路,而无需任何外部端接。正确测量PCIe参考时钟上的抖动并不容易,因此为简化流程并消除混淆,Silicon Labs开发了PCIe时钟抖动工具。

8、定制:Silicon Labs的ClockBuilder Pro软件工具可指导用户轻松、逐步地生成针对您的时钟树要求的配置文件。配置文件完成后,ClockBuilder Pro可针对用户的设计专门分配一个定制部件号,提供相关数据表附录,并允许用户将其保存以备后用。

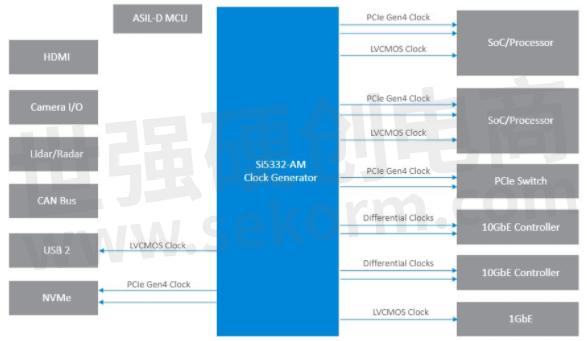

方框图

合适的Silicon Labs产品列表

- |

- +1 赞 0

- 收藏

- 评论 1

本文由宝丁转载自Silicon Labs,原文标题为:汽车ADAS和自动驾驶,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【应用】可编程任意频率时钟发生器Si5332简化了板级FPGA设计

Silicon Labs推出的Si5332任意频率的时钟发生器提供最高级别的集成,实现在 10/25/100G 数据中心、通信和工业应用程序中的完整时钟树整合。本文介绍了可编程时钟在FPGA设计中的应用

【应用】SDI编解码技术应用之基于高精度时钟发生器的高清视频同步系统设计

在SDI高清视频系统中,我们运用世强代理的Silicon Labs公司系列高精度时钟发生器Si5324,Si5332,Si5338,Si5341,Si5345,Si552等,来组建起整个SDI同步系统。产品覆盖了SD-SDI,HD-SDI,3G-SDI,6G-SDI,12G-SDI等标清、高清和超清的各种SDI标准高低端应用,为SDI设备提供最优的时钟性能。

【应用】基于Si5332时钟发生器的PHY接口器件参考时钟,实现一站式时钟芯片设计

由于F104S8A是搭配CPU进行设计的,与F104S8A以QSGMII接口实现通信,这些CPU比如LS1046A、LS2080A本身均需要多个参考时钟源,这些时钟源包括常用的系统时钟、本地总线时钟、DDR时钟、SSD固态硬盘接口时钟等,采用Silicon Labs SI5332时钟发生器作为F104S8A的参考源可以兼顾给CPU提供其它参考时钟,可以实现一站式时钟芯片设计。

【产品】最具频率弹性可编程的CMOS时钟发生器Si5351,非常适用于对成本敏感的消费性电子应用

Si5351采用优异的时钟技术,非常适用于对成本敏感的消费性电子应用,可在不牺牲性能的情况下大幅降低系统成本、功耗并能满足空间需求。

【经验】如何使用CBPro软件配置时钟发生器Si5332的晶体输入端电容

Silicon Labs的时钟发生器Si5332支持外置晶体/晶振/参考时钟输入,也支持内置晶体的版本,目前使用较多的是内置晶体版本,但部分用户在设计时由于自身需求仍然选择外置晶体,而选择外置晶体时通常会发现配置的晶体无法正常启动或者启动时间不太理想,如果使用CBPro软件适当配置Si5332,可以避免大部分问题。本文就将介绍如何使用CBPro软件配置Si5332的晶体输入端电容。

【视频】奥拉包含JA、Buffer、NS和时钟发生器在内的多品类时钟器件,抖动值最小可达80fs

奥拉 - BUFFER,去抖芯片,青年成就组织,高频可编程晶振,JA,时钟发生器,缓冲器,AU5331,AU5411,AU526X,AU5410,AU5325,AU5424,AU524X,AU5415,AU5327,AU5426,AU5417,AU5329,AU5508,光模块,车载通信,雷达,传输线卡,虚拟现实,高清视频,ADAS,VR

Silicon Labs(芯科科技) Si5351A/B/C-B可编程时钟发生器数据手册

Si5351是一款基于I2C的可编程时钟发生器,适用于替代晶体、晶振、VCXO、PLL和缓冲器。它具有高精度频率合成能力,可生成高达200 MHz的非整数相关频率,并提供多种输出选项和配置功能。

SILICON LABS - I²C可编程任意频率CMOS时钟发生器+VCXO,晶体及时钟芯片,评估板,I²C-PROGRAMMABLE ANY-FREQUENCY CMOS CLOCK GENERATOR + VCXO,EVALUATION BOARDS,SI5351A,SI5351B,SI5351A-B-GTR,SI5351C,SI5351B-B-GM,SI5351A-A-GT,SI5351C-A-GM,SI535X-TMSTK,SI5351C-B-GM,SI5351B-B02073-GM,SI5351X-BXXXXX-XXX,SI5351B-BXXXXX-GM,SI535X-B20QFN-EVB,SI5351C-B-GMR,SI5351A-B-GM,SI5351A-B-GT,SI5351-B,SI5351,SI5351A-BXXXXX-GM,SI5351A-B-GM,SI5351C-B,SI5351A-B,SI5351B-B-GMR,SI5351B-B,SI5351A-B-GT,SI5351A-BXXXXX-GT,SI5351C-BXXXXX-GM,室内照明,AUDIO/VIDEO EQUIPMENT, GAMING,住宅大门,手机相关,音频/视频设备、游戏,高清电视、DVD/蓝光、机顶盒,HDTV, DVD/BLU-RAY, SET-TOP BOX,电脑外设,智能家居,SERVERS, STORAGE,玩具,HANDHELD INSTRUMENTATION,服务器,存储,个人代步工具,便携数码,消费电子部件,通信设备,PRINTERS, SCANNERS, PROJECTORS,网络/通信,电脑,工业电子,打印机、扫描仪、投影仪,个人娱乐,手持仪器,XO REPLACEMENT,可穿戴设备,RESIDENTIAL GATEWAYS,NETWORKING/COMMUNICATION,XO替换

【经验】新型时钟发生器SI5332的多个用户GPIO接口设置用例

SI5332是Silicon Labs推出的一款新型时钟发生器芯片,是一款用于电信传输网、政企网、基站、数据中心、消费电子等多行业通用的时钟芯片。这款时钟发生器芯片是比较成功的,SI5332拥有超低的jitter性能指标(RMS JITTER 230 fs)、可输出路数多(多达12路)、支持任意频点输出、采用模拟环(上电初始化时间快)、可内置多组频率计划等特点,获得了市场及大部分工程师的认可。SI

【经验】Silicon Labs时钟发生器SI5332时钟差分信号变单端输出问题及处理方法

Silicon Labs时钟发生器SI5332在使用CB Pro软件配置好电平之后,有工程师会有疑问,原本配置好的3.3V 125MHz lVDS电平 OUT/OUTB是否可以在配置不动的情况下单独分开做两个125MHZ单端时钟输出?本文将为你解析。

【经验】如何实现差分时钟发生器在线编程时钟输出?

SI5338任意可编程时钟发生器是Silicon Labs推出的一款差分时钟发生器,SI5338可进行任意比率、任意输出频率合成,从而作为一个设备可以替代多个晶体振荡器和固定频率时钟发生器。目前在光通信、服务器、物联网等行业仍然有大量的应用。

【产品】可提供4个PCIe时钟输出的PCIe时钟发生器,支持100MHz的串行ATA(SATA)

Si52144是一款由Silicon Labs(芯科科技)推出的支持扩频的PCIe时钟发生器,可以提供4个PCIe时钟和25 MHz参考时钟,符合PCI-Express Gen 1,Gen 2,Gen 3,Gen 3 SRNS,Gen 4标准。该器件具有四个用于使能输出的硬件输出使能引脚,以及一个用于控制PCIe时钟输出上的扩频的硬件引脚。 除硬件控制引脚外,I2C可编程性还可用于动态控制。

【经验】时钟发生器Si5332接地PAD引起的频率计划烧录失败问题及解决方式

Si5332支持多个输出端,每个输出端有独立的输出电压,使用ClockBuilder Pro可以快速轻松地配置频率计划,并且有专门的烧录器可通过I²C接口烧录到芯片内的NVM,但是有时候接地PAD引起的频率计划烧录失败,本文将简要分析。

时钟缓冲器选型,输出26M 27M 100M 125M时钟,输出类型是LVDS

您好,您可以看看芯科的Si5330x系列,输出1M~725MHz,输出类型含括LVDS、LVCMOS等,资料可参考:https://www.sekorm.com/doc/1316339.html

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

【经验】如何对时钟发生器Si5332进行烧录

Si5332是Silicon Labs公司推出的一款经典的时钟发生器产品。本文将主要介绍如何对这款产品进行烧录。首先把ClockBuilder Pro Field Programmer烧录工具和烧录座连接,使用USB线缆与电脑连接;然后打开ClockBuilder Pro客户端工具,最后一步就是对Si5332进行烧录操作。

电子商城

现货市场

服务

可定制Wafer连接器、牛角连接器、FPC/FFC 连接器,IDC 连接器的尺寸/规格等参数,电流不超过8A;环境温度:-40度~105度;寿命/拔插次数:不超过800次。

最小起订量: 5000 提交需求>

可来图定制均温板VC尺寸50*50mm~600*600 mm,厚度1mm~10mm,最薄0.3mm。当量导热系数可达10000W/M·K,散热量可达10KW, 功率密度可达50W/cm²。项目单次采购额需满足1万元以上,或年需求5万元以上。

提交需求>

登录 | 立即注册

提交评论