【经验】EPC推出的用于氮化镓器件的LGA和BGA封装寄生电感低、尺寸小和热性能出色,应用时需考虑相关制造和设计事项

当EPC的客户表达对功率半导体器件(晶体管、二极管或集成电路)有更好封装的愿望时,他们的要求可以分为以下六类:

1.封装可以小一点吗?

2.封装寄生电感可以降低吗?

3.产品的导通损耗能不能更低?

4.封装的热效率可以更高吗?

5.产品的价格可以更低吗?

6.封装可以更可靠吗?

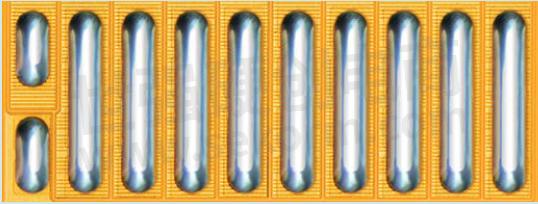

EPC的氮化镓晶体管和集成电路采用了非常不同的方法来封装功率半导体-EPC完全放弃了以前封装,因此同时改进了上述所有六个要求。EPC的创新晶圆级、平面网格阵列(LGA)封装和球栅阵列(BGA)封装实现了功率密度方面的最新技术水平。图1显示了EPC2001C的安装侧照片,该EPC2001C的焊盘间距为0.4mm,而EPC2045的焊球间距为0.5mm。

图1(a):EPC2001C的安装侧[2]。

图1(b):EPC2045的安装侧。

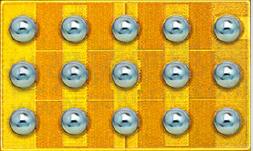

广泛的测试证明,氮化镓场效应晶体管和IC在应用电路中被正确设计时,它们是可靠的。事实上,在2010年至2017年间,在该领域实际使用总时间超过300亿小时内总共只有127个设备故障,其中的75个故障是由于组装技术差或印刷电路板(PCB)设计的比较差。图2的图表显示了这127次故障的细分。

图2:在实际应用超过300亿小时后,eGaN器件仅经历过三(3)次与器件相关的故障。故障的最大原因是装配不良。

确保高可靠性并发挥eGaN器件的最大性能,重要的是要遵循一些简单的PCB设计和装配指南,这些指南在本应用手册中已经以实际的示例出现,如果没有遵循这些指导方针,那么就会出现问题。

注意:任何与此处推荐的钢网厚度/锡膏组合有偏离,应联系EPC以协助开发。

概述

对于可靠、高良率的装配,LGA或BGA eGaN器件必须:

1.为每种锡膏定义正确的PCB阻焊层(SMD)封装,以确保在干净的PCB表面上正确容纳锡膏。

2.要有正确的焊锡量和回流焊工艺来提供足够的高度来正确的冲洗焊盘之间的任何焊剂,但锡膏不要过多,否则连接处会变得不稳定并倾斜甚至在回流焊期间失败。

3.将焊盘之间的所有助焊剂冲洗干净,并在通电前晾干。

4.如果部件在使用过程中会暴露在湿气中,请使用底部填充剂。

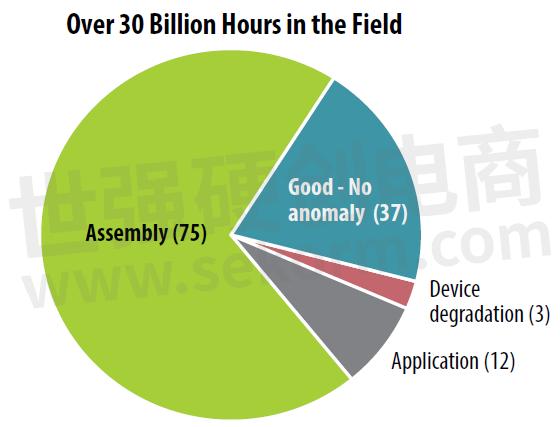

图3显示了正确安装的器件器件器件的侧视图。

图3:正确安装的eGaN器件(侧视图)。

eGaNFETs和IC的印刷电路板设计注意事项

功率设计人员可能不像他们的数字电路同行那样熟悉细引脚间距器件。本节将涵盖设计人员在为eGaN器件设计封装时需要考虑的许多设计事项。

将eGaN器件连接到PCB的焊点的质量对于可靠的电气、热和机械连接至关重要。定义焊点质量的因素包括对称性、体积、高度和光洁度。主要关注布局的设计人员可能会忽略这些因素,因此器件制造商必须负责在其产品数据表中提供清晰和简单的指南。这些指南包括推荐的封装(铜尺寸和阻焊层开窗)和锡膏钢网设计。

1.阻焊层定义焊盘

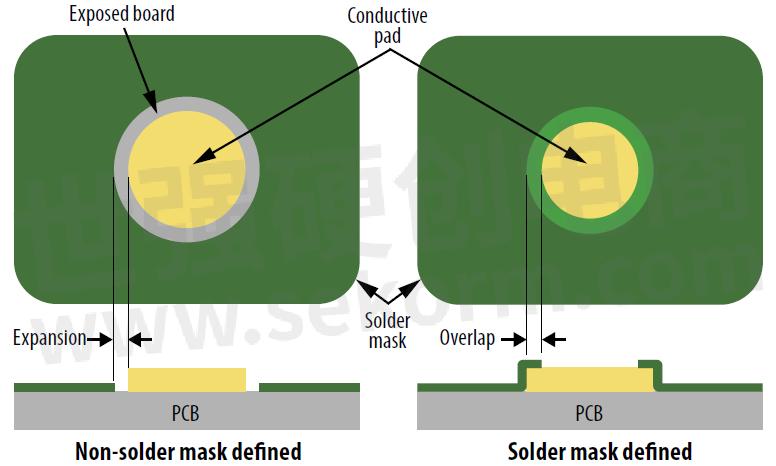

对于eGaN器件,推荐LGA和BGA焊点采用图4(右)所示的阻焊层定义(SMD)。图4(左)显示了通常用于PCB设计的非阻焊层定义(NSMD)封装焊盘。在EPC对客户装配设备故障的调查中,EPC发现了一些情况,PCB制造商会修改Gerber文件以适应其为更大封装开发的内部制造设计指南,从而会覆盖客户所提供的设计。

图4:阻焊层定义与非阻焊层定义的焊盘。

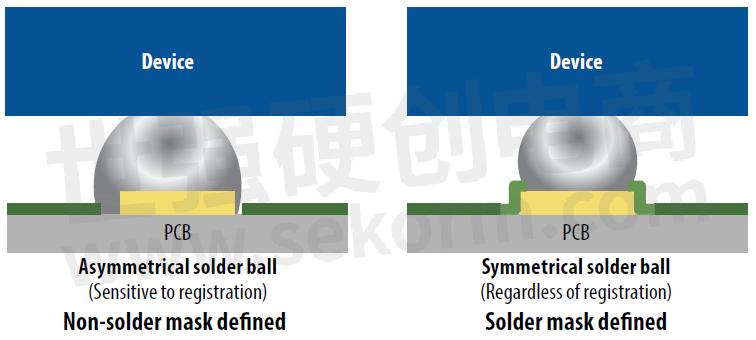

在最终电路板发布之前进行设计审查,会在组装过程中产生报废或返工费用之前突出这个问题。图5显示了SMD焊盘如何通过确保焊接后的对称焊点来降低机械应力。相比之下,使用NSMD封装会导致不对称的焊点,因为不可能在铜层和掩膜层之间实现100%的完美对齐。在SMD封装的情况下,可在PCB的制造公差范围内确保抗扰度。

图5:在焊球对称上铜对阻焊层对齐的影响。

2.阻焊层质量

并非所有阻焊层都是相同的,重要的是要知道在谈到阻焊层时如何做才能得到高质量PCB,其厚度和一致性是最重要的。如果阻焊层太厚,随着锡膏需要压入的距离变大,很难正确分配锡膏。

如果阻焊层的一致性不均匀,由此可能会让焊点影响钢网正确地装在板上。阻焊层缺陷或过多的阻焊层开窗会导致焊点高度降低,并在极端情况下导致开裂和或芯片倾斜甚至开路。产生的变形焊点将在冷却中伴随着机械应力增加,这会加速热引起的故障。

适用于采用eGaN器件的PCB的阻焊层符合IPC-SM-840T等级,例如Taiyu 4000HFXL.P.I,PSR-2000/LF02/CA-25或同等产品。在PCB制造文件中明确说明阻焊层不会被PCB制造商放大或修改,这一点很重要。

应使用激光直接成像(LDI)将阻焊层按主图纸中指定的公差或相对于铜层2mils进行设置。最后,阻焊层不应被裁剪。裁剪更加依赖设计人员来确保布局软件具有正确的设计规则设置以及正确设计的封装。

3.焊点体积

电路板和器件之间的焊点高度对机械应力也很关键。焊点的高度确信会影响可靠性、电气和热性能之间的平衡。如果焊点高度太低,器件将承受高热引起的机械应力,这将导致焊球或焊点金属疲劳。安装得太高的器件将承受更高的电应力和热应力(由于PCB的热提取效应降低)[3]。

每个器件的最佳高度不同。对于LGA和BGA器件,各种锡膏类型等附加选项必须是设计决策的一部分。图6显示了不同的锡膏类型如何得到不同的钢网设计。应该注意的是,如果客户希望对第3类和第4类锡膏使用相同的阻焊层,EPC可以与客户一起提供可能适用于两种锡膏类型的建议。此类建议也将显示在数据表中。

图6:锡膏类型对钢网设计的影响。

4.焊盘表面处理

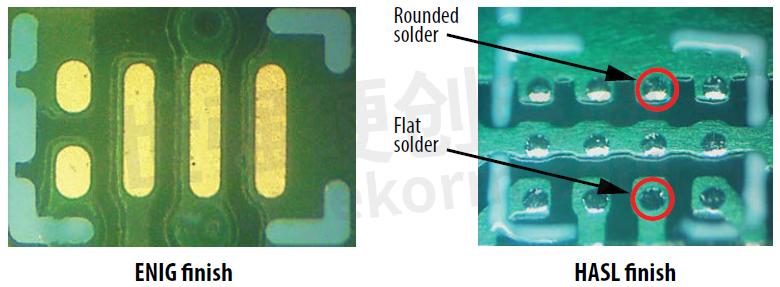

许多设计人员选择为他们的电路板使用热风整平表面处理(HASL),这会将锡膏沉积在焊盘上。这些锡膏沉积物会在焊盘上产生少量锡膏,从而增加原本要通过钢网分配的锡膏量。这种增加的锡膏将包含在焊点锡膏量中,最终影响完成的焊点体积,从而影响其质量。

此外,HASL工艺不精确,通常会在不同数量的焊盘上产生不均匀的锡膏,如图7所示(右)。这可能导致芯片倾斜或焊接点开路。建议使用无电镀镍沉金(ENIG)焊盘表面处理,可产生非常均匀且平坦的焊盘,如图7(左)所示。

对于ENIG表面处理,建议使用150微英寸的典型镍(Ni)厚度和3-5微英寸的金(Au)厚度,符合IPC-4552。

图7:ENIG表面处理相比HASL表面处理显示不均匀的焊点高度。

5.丝印

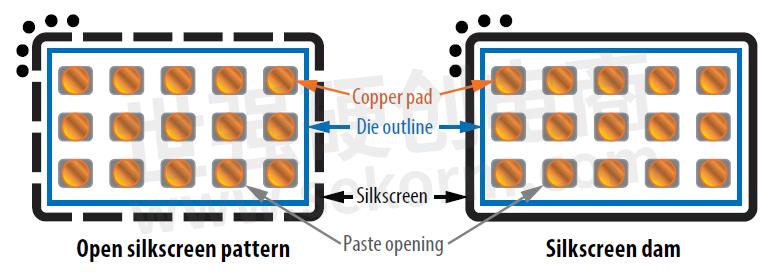

虽然丝印传统上在PCB中的作用很小,但它可以成为可靠性功能的一部分,因为它的厚度不为零,因此会阻碍回流焊过程中助焊剂的流动。

如果回流焊期间助焊剂流动受阻,可能会导致芯片倾斜和助焊剂残留。丝印还用于在装配过程中正确对准芯片,许多设计人员倾向于设计一个全封闭的丝印图案来勾勒器件的轮廓,如图8(右)所示。当焊剂在回流焊期间不能从芯片下方流出时,这可能会导致阻塞,并且对于围绕整个或大部分芯片延伸的厚丝印尤其严重。助焊剂阻塞会导致未固化的助焊剂出现在芯片下方,并可能导致热和电气枝晶形成(请参阅下面的故障排除部分)。

如图8(左)所示,只需在不同位置打开丝印墙即可防止阻塞。丝印也可能是焊盘污染的来源,并且应注意避免这种情况。丝印也应该尽量薄,厂商能做到远低于1mil(大概在0.7mil的范围内)。

图8:具有开放式器件轮廓丝印(左)和封闭式丝印器件轮廓(右)的器件焊盘图案。

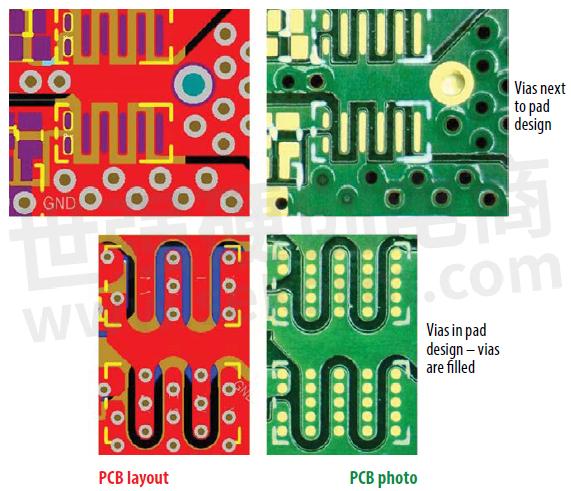

6.过孔

过孔由于其小尺寸和电气性能要求[4]而成为eGaN器件PCB设计中不可或缺的一部分。过孔尺寸由设计人员自行决定,他们需要根据过孔的使用方式了解一些限制。

基本的过孔是用于PCB各层之间的垂直连接,由带有铜圆环的孔组成。制造限制将孔尺寸限制为最小6mils,最小圆环尺寸为5mils。设计人员可能会认识到,这已经超出了某些eGaN器件焊盘间距的尺寸,并且可能会在一个方向上做出妥协。芯片附近的过孔应始终盖油(用阻焊层覆盖),以防止锡膏在回流焊过程中吸到孔中,并防止由于靠近芯片的裸露铜而导致电压间隙问题。

在某些情况下,可能需要在器件焊盘下方放置过孔。如果需要,必须对过孔进行填充和封盖,以防止最佳焊点高度所需的锡膏在回流焊期间流入孔中。需要进行封盖以防止填充物在锡膏焊盘下放气。该过孔应在布局设计软件中盖油,以便焊盘阻焊层开窗,它应与过孔重叠,从而决定覆盖或暴露过孔的哪些部分。完成的过孔必须与焊盘的其余部分具有基本相同的高度。这将确保正确分配锡膏。

某些设计可能需要许多过孔,这些过孔用于分配电流并增加流向另一层的总电流。尽管过孔连接到同一个电气节点,但制造限制要求过孔的边到边间距至少为10mil,以防止电路板穿孔破损并确保电路板厚度均匀。对器件附近的或内部的过孔盖油,可能会导致高点,从而导致钢网被垫高,并可能导致在制造过程中锡膏过度沉积。在器件附近或内部使用过孔时,请确保PCB制造商了解您的钢网安装问题。

某些设计可能具有最小过孔尺寸限制,这意味着无法将过孔放置在器件的焊盘下方,必须将其放置在器件旁边,例如图9(上)所示的示例设计。图9(下)显示了一个没有焊盘内过孔限制的设计,照片清楚地显示FET焊盘已被电镀,并且无法再看到过孔。

图9:在晶体管旁边有过孔的布局设计(上)和在晶体管焊盘内有过孔的布局设计(下)。

7.层定位

组成PCB的许多层需要相互对齐(定位)。这确保功能板是正确的,并通过提供定位公差来进行说明。相同类型的层通常与不同类型的层的公差说明也不同。通常相互定位的层是铜对铜、铜对阻焊层、铜对孔和铜对丝印(通常不指定,但有助于芯片放置)。

大多数层可以指定为相对于铜层2mils的定位公差,但孔除外,它应至少使用3mils的定位公差。

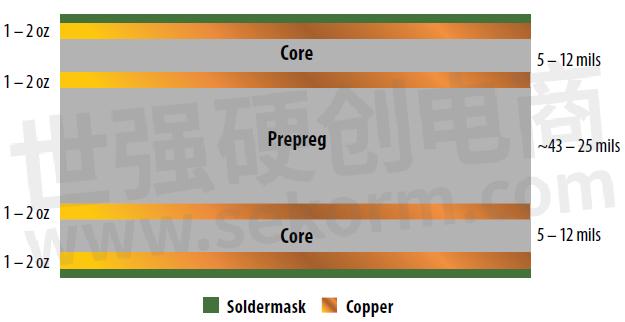

8.叠层

叠层定义了构成PCB的每一层的厚度。用于eGaN FETs和ICs的PCB通常使用1和2盎司(35和70微米)之间的铜厚度,具体取决于设计和所需的电流密度。绝缘层通常使用FR4或FR370-HR等材料制成。具有较高玻璃态转化等级(Tg至少为180°C)的基材对于更高的可靠性是首选。

可制造性和电气性能之间的平衡决定了绝缘层的厚度。100V器件的最佳布局规定第1层(例如顶层)和第2层的芯板之间的厚度为5-mil。由于对称性要求,这也将迫使第3层和第4层的厚度为5-mils,半固化片被调整为满足最终的电路板厚度(通常为1.5毫米或62mils)。对于更高电压的器件,为了确保适当的“爬电”要求,建议的最小芯板厚度为12mils。然后半固化片将调整到大约25mils。图10显示了典型的PCB叠层。

图10:适合eGaN器件的典型的PCB叠层。

9.电路板平整度

一个鲜为人知的PCB规范是电路板平整度。它仍然是一个重要的规范,因为过度弯曲的电路板可能会阻止钢网正确地安装在电路板上,从而可能导致无法在焊盘上正确分配锡膏。最大水平或垂直尺寸为200毫米(8000mils)的阵列应指定平面度在每米40毫米(每英寸7.5mil)以内。

10.基准点

基准点用于组件贴装过程中的元件定位。由于eGaN器件的细间距,通常需要在PCB上添加基准点。有两种类型的基准点,全局基准点和局部基准点。全局基准点用于定位PCB拼板阵列,局部基准点用于单个板上。大多数设计都需要局部基准点来调整eGaN器件。

一个典型的板子上应至少有三(3)个基准点,其中至少有两(2)个垂直对齐,两(2)个水平对齐。基准点应放置在尽可能靠近板边缘并尽可能远离彼此的位置。这种放置改善了更长距离的定位。如果eGaN器件更多地位于电路板的一侧,则基准点应彼此靠近。对于大多数装配来说,一个40-mil直径的基准点应该足够了。

11.单个电路板或拼板尺寸限制

使用eGaN器件的PCB和PCB拼板应限制尺寸。较大的电路板在精确组装具有较小特征尺寸的eGaN器件更难以定位。单板和拼板应限制在单边200毫米。对于拼板,建议旋转电路板,以尝试将各种电路板的所有eGaN器件放置在尽可能靠近的位置。这使得可以使用更大的电路板,然后定位位置仍然可以尽可能靠近eGaN器件。

eGaN器件的装配过程

到目前为止,讨论的重点是PCB设计及其可制造性。在本节中,将介绍与PCB齐头并进的装配过程。

12.锡膏选择

EPC目前使用Kester NXG1 Type3 SAC305和Kester NP505-HR SAC305 Type4锡膏来焊接eGaN器件。两种锡膏都是含88.5%金属的免清洗助焊剂。

为防止形成热枝晶和电枝晶,即使使用免清洗助焊剂,也建议从板上清洗助焊剂。EPC使用由Technical Devices Company制造的Nu/Clean AquaBatch XL标准系统中的Kyzen Aquanox® A4625化学品,用于去除免清洗助焊剂。

如果使用免清洗助焊剂且未冲洗干净,则回流后在150°C下烘烤至少60分钟。这可确保免清洗助焊剂正确固化并有助于防止枝晶形成。

如果使用水冲洗助焊剂,则需要冲洗eGaN器件的所有四个侧面,以确保正确去除助焊剂。倾斜的设备会阻碍液体的流动冲洗并导致助焊剂留在钢网下方。因此,建议使用离子含量低的免冲洗助焊剂,然后再冲洗免冲洗助焊剂。

13.钢网设计

推荐使用100微米厚的激光切割不锈钢钢网。光滑的壁激光切割钢网更有可能释放所需的分配量。3类锡膏需要比4类锡膏有更大的开口,参考[15]为这两种锡膏和每种芯片配置都提供了建议。在必须使用冲压钢网的情况下,可能需要稍微扩大开口以补偿适当的锡膏释放量。

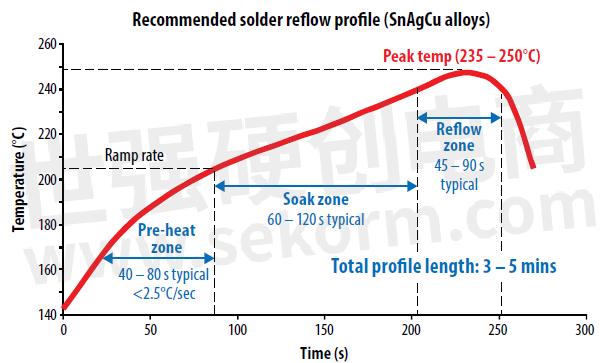

14.回流曲线

图11显示了根据锡膏制造商对锡膏的建议为eGaN器件推荐的回流焊接曲线。对于所使用的锡膏,应始终遵循供应商推荐的回流曲线。

图11:推荐的回流焊接曲线。

PCB设计和装配问题的故障排除

如果不遵循正确的PCB设计规则,可能会出现许多问题。不良的组装技术可能会加剧这些问题。本节介绍了EPC遇到的许多问题并解释了它们的起源。

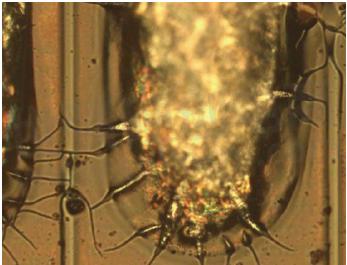

15.电气枝晶

电气枝晶被认为是当助焊剂暴露于电压并形成导电晶体时形成的离子污染[5]。电压越高,枝晶形成越快。电气枝晶会很快导致故障,因为它们在形成过程中除了会产生短路外还会产生大量热量。图12显示了在eGaNFET的焊点周围形成枝晶的示例。

图12:显示eGaN FET暴露于残余助焊剂后形成的电气枝晶。

16.热枝晶

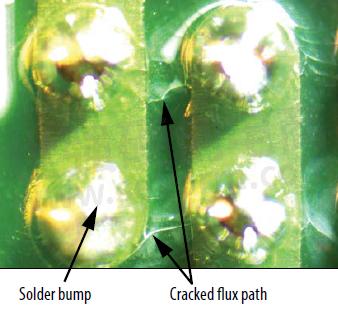

热枝晶是一个相对较新的发现,不要与电枝晶混淆,尽管它们可能看起来相似。它们是由炉子冷却过程中形成的助焊剂裂纹引起的。未冷却的锡膏会扩散到助焊剂裂缝中。这些焊丝可以显著减少焊盘之间的电气距离,并且在工作过程中可能会击穿。即使在使用免清洗助焊剂的情况下,在装配过程之后助焊剂裂纹仍然存在。图13显示了在没有芯片的情况下形成的PCB上的助焊剂裂纹。

图13:没有芯片的情况下残留助焊剂裂纹形成热枝晶路径示例。

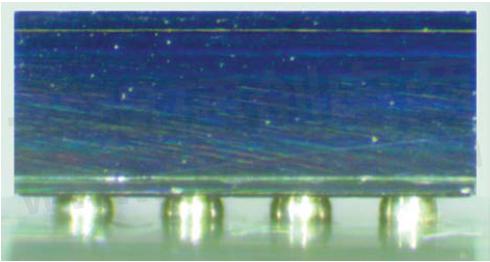

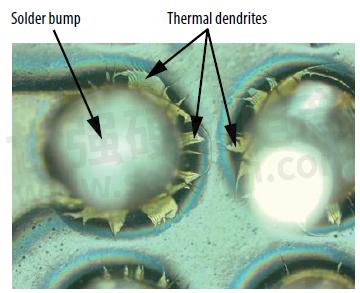

热枝晶与在金属熔体中看到的传统热枝晶略有不同,其中成核源的存在会导致“臂”从过冷液体中的颗粒中生长出来,形成枝晶[6,7,8]。这种枝晶可以通过清洗免清洗助焊剂来防止或去除。图14也显示了热枝晶的示例。

图14:eGaN IC 显示在破裂的残余助焊剂中形成热枝晶。

17.焊点附着力差

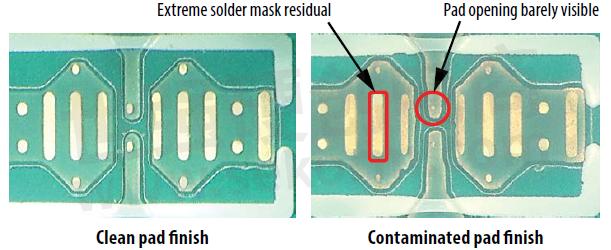

受污染的焊盘会导致焊锡附着力差、空洞和大的不上锡区域。大多数污染来自于不良的PCB制造工艺,其中阻焊层残留在焊盘上,例如来自受污染的清洁液。阻焊层渗漏和丝印残留物也是焊盘污染的常见来源。

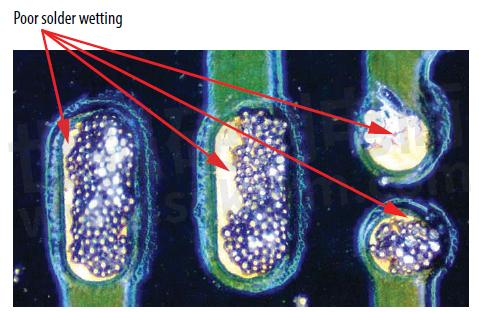

图15显示了清洁焊盘面(左)和严重污染的焊盘面(右)的示例。焊锡附着力差会导致开路,并且在具有高电流能力的器件中,会导致电流密度过大,因为电流被迫流向不确定的方向,最终导致器件故障。图16显示了上锡问题的示例。

图15:清洁的焊盘面和污染的焊盘面的示例。

图16:较差的焊锡示例。

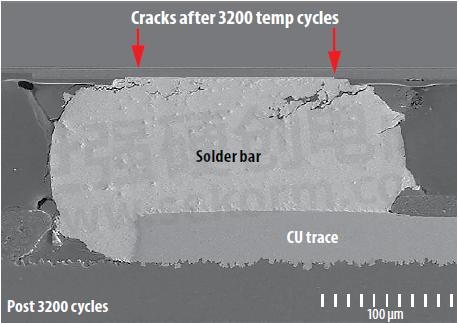

18.焊盘开裂

焊盘开裂主要是由于热引起的机械应力。如果在装配过程中焊点在应力作用下变硬,它会导致加速失效,因为变硬产生的应力会被添加到由热膨胀和收缩引起的应力之上。

用于热循环期间焊点剪应变的著名行业分析模型[9]是:

其中:

ε=焊点剪应变

Δα=芯片和PCB之间的热膨胀系数差[°C-1]

ΔT=循环温度波动[°C]

DNP=焊点与芯片中心之间的距离(基于芯片尺寸和焊点/焊盘位置的应力中心)[m]

h=焊点高度[m]

等式1表明非常高的焊点高度会将热感应应力降低到接近零,这并不总是可行的。热感应应力和可靠性之间的平衡通常由器件制造商确定,并在产品数据表中给出。对于eGaN器件,阻焊层定义的焊盘进一步降低了回流过程中产生的应力。

图17显示了锡膏焊点开裂的示例。

图17:eGaN IC焊盘的横截面X射线显示焊盘破裂。

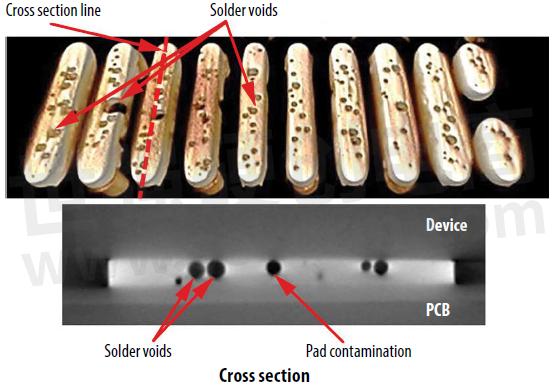

19.焊点空洞

焊点空洞是焊点内的中空体积,如图18所示。焊点空洞可能有多种原因,包括焊点与焊盘的粘附性差、回流期间受污染焊盘的放气、器件间隙高度不足[10]以及焊点不正确配置。

空洞减少了器件和PCB焊盘之间的接触面积并引起焊点内不均匀的机械应力和热引起的应力。随着时间的推移,这些空洞会增长并导致失效。

图18:eGaN FET的3D-X射线显示过多的焊点空洞(上) 焊盘与焊点界面上的污染物导致空洞形成(下)。

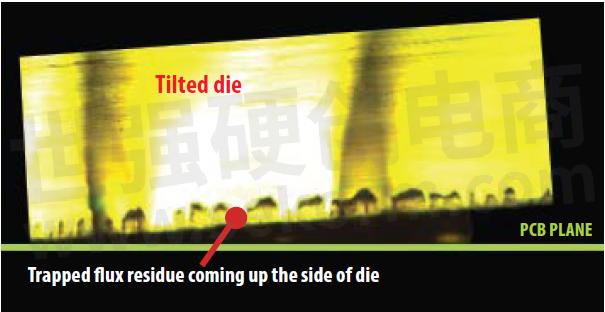

20.芯片倾斜

芯片倾斜可能由多种原因引起,例如焊点附着力差、锡膏不均匀涂敷、回流焊接时振动过大、温度曲线未优化、阻焊层过大或锡膏钢网开孔过大。芯片倾斜不利于器件可靠性,因为它会导致芯片上的热机械应力不均匀。它也可能是短路或开路焊点的迹象。图19显示了eGaN器件倾斜的示例。

图19:焊接后芯片严重倾斜的eGaN器件的侧视图。

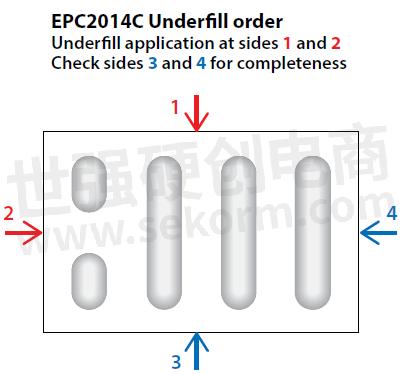

21.底部填充

底部填充应用于电路板暴露在潮湿环境中的应用。水分和其他污染物可能会提供允许枝晶生长的环境。对于支持150ºC的EPC器件,一些可用的底部填充剂是Hysol FP4531、Namics U8437-2、Namics 8410-406B和Henkels Loctite Eccobond UF 1173。根据供应商的建议,在应用底部填充剂之前,芯片表面应该没有任何助焊剂残留物。在选择应用底部填充的芯片侧面时,必须考虑焊盘布局的方向性。

22.设计实例

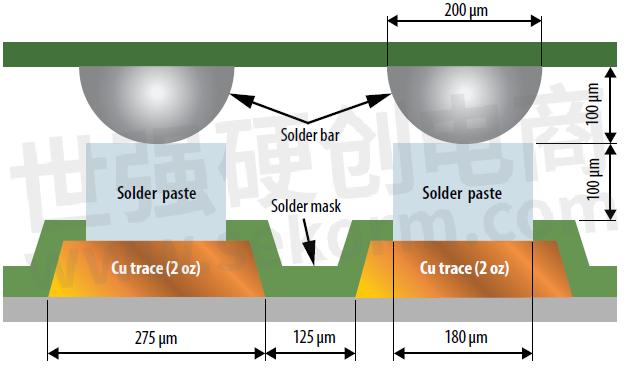

图20是采用LGA封装(也适用于BGA封装)的EPC2001C和NC257-2 SAC305[13]的横截面图,无铅、免清洗锡膏涂在顶层金属层为两盎司铜厚的PCB上面。横截面区域将用作焊料用量的代表。根据数据表,焊接点半径为100μm,横截面积为15.7nm2。使用NC257-2 SAC305无铅、免清洗、类型3锡膏,金属含量为88.5%,钢网厚度为100-μm,阻焊层宽度约为180μm。

图20:具有代表性的PCB安装的横截面,使用EPC2001C(预回流)。

23.检查

eGaN器件机械结构坚固,并在批量装配中表现出高良率。然而,如果不采取一些标准预防措施来确保足够的焊接回流、减少过度的芯片倾斜并避免残留未固化的助焊剂,损坏仍然可能发生。

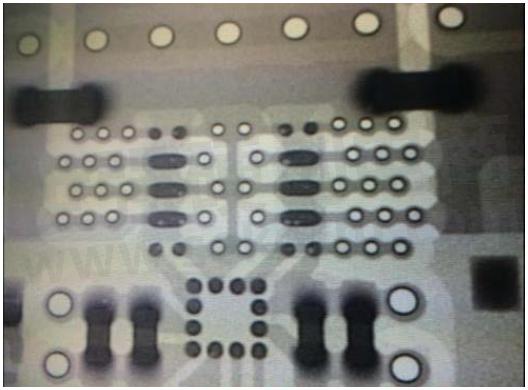

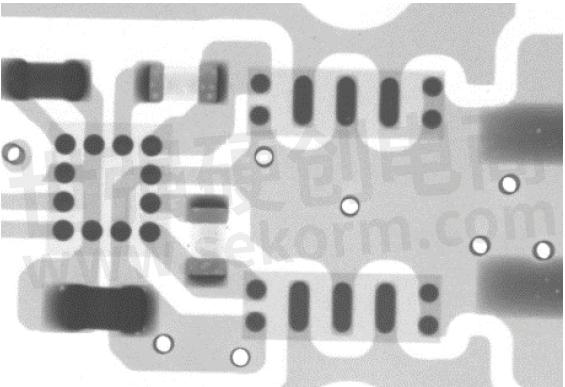

尽管eGaN器件的设计使得回流焊接肉眼可见,但确定器件是否已正确回流的最佳方法是生成X射线图像。图21和22显示了采用焊接钢网工艺装配的EPC2019的X射线图像。图21显示了带有空洞和形状不规则的焊接点的图像,表明可能存在焊点大小或回流问题。如图22所示,最小的空洞和一致的焊接点代表了高可靠性以及出色的热和电气特性。

图21:显示EPC2019和LM5113驱动器的电路板的X射线。该图显示了焊点中的空洞以及EPC部件和驱动器中看起来不规则的连接点外形。这是可能的锡膏量或回流问题的示例。

图22:正确回流的EPC2019和LM5113驱动器的X射线图。EPC部分或驱动器中没有明显的空洞。连接点是纯黑色,连接点形状的大小非常一致,十分规则。

24.清洗

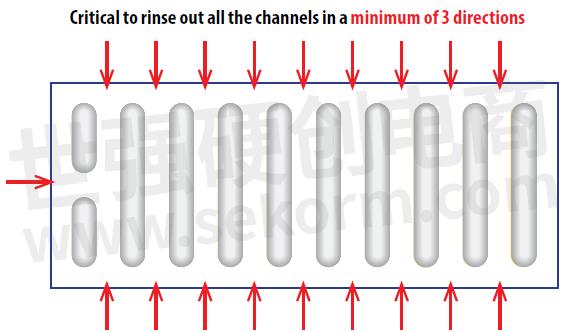

如果装配过程使用需要清洗的助焊剂的锡膏,芯片倾斜会阻碍清洗液的流动,导致助焊剂被困在芯片下方。这种残余助焊剂会导致枝晶的快速形成(图12),这将导致器件早期故障。因此,建议使用离子含量低的免冲洗助焊剂,然后再冲洗免冲洗助焊剂。一些EPC设备需要以特定方式冲洗,以正确清洁钢网下方。应注意适当冲洗零件以去除助焊剂。图23所示的示例是EPC2001C型芯片,需要在至少三个侧面进行冲洗以充分清洗掉助焊剂。

图23:EPC2001C芯片示例和正确清洁掉助焊剂需要的最少冲洗次数。

关于LGA和BGA封装

器件不含铅和卤素。符合RoHS标准的LGA和BGA封装使用成分为95.5%的Sn、4%的Ag、0.5%的Cu的Sn/Ag/Cu锡膏或成分为97.5%的Sn、2.5%的Ag的Sn/Ag锡膏。所有无铅产品的湿度敏感度等级为1(MSL1260ºC),即最高的商业半导体等级。

在处理EPC eGaN FETs和ICs时,应采取正常的制造中ESD预防措施。编带和卷盘的推荐仓库存储条件:温度20℃至28℃,湿度40%至60%。

快速启动工程实验室装配

EPC的eGaN器件可以直接安装到PC板上,无需焊接,方法是在回流焊接时使用粘性助焊剂将部件固定到位。可接受的无铅(PbF)工艺示例使用Kester TSF6502免冲洗助焊剂。EPC网站的组装页面上提供了快速参考芯片连接和拆卸说明以及视频。

总结

LGA和BGA封装提供了充分利用eGaN技术能力所必需的低寄生电感、小尺寸和出色的热性能。通过适当的制造技术,使用eGaN器件的组件将具有高产量和长而可靠的工作寿命。

LGA和BGA器件封装必须定义阻焊层。阻焊层设计应根据数据表上推荐的焊盘图案。

正确的焊点大小和回流曲线将有助于确保安装的芯片保持水平,并具有足够的间隙以进行正确的冲洗。需要在各个方向进行冲洗和干燥,以去除会导致枝晶生长的残留物。必须调整回流温度曲线以确保完全回流并帮助避免芯片倾斜。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由叫我大表哥吧翻译自EPC,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

How2GaN | 如何设计具有最佳布局的eGaN® FET功率级

eGaN FET的开关速度比硅基MOSFET更快,因此需要更仔细地考虑印刷电路板(PCB)布局设计以最小化寄生电感。寄生电感会导致过冲电压更高,同时减慢开关速度。本篇笔记将会探讨使用eGaN FET设计最佳功率级布局的关键步骤,来避免上述不良影响并最大化转换器性能。

【经验】EPC eGaN FET和eGaN IC PCB封装设计指南

一个良好的PCB封装设计对于GaN器件的一致性和可靠性是很重要的。本文是根据数据手册为EPC器件设计正确封装的指导原则——以EPC2016C和EPC2045为例,分别从LGA和BGA封装来完成介绍。

【经验】与前代eGaN FET保持“相容”同时,宜普第二代增强型无铅eGaN®FET提供更优异性能

无铅eGaN FET中EPC2XXX系列技术资料,帮助工程師利用宜普产品设计最优异性能产品或解決方案,产品系列包括EPC2001、EPC2007、EPC2015、EPC2014、EPC2010及EPC2012。

EPC eGaN®FET/晶体管选型表

EPC提供增强型氮化镓半桥功率晶体管/增强型功率晶体管/功率晶体管的选型:配置:Dual Common Source、Dual with Sync Boot、Half Bridge、Half Bridge Driver IC、HS FET + Driver + Level Shift、Single、Single - AEC Q101、Single – Rad Hard、Single with Gate Diode、Single with Gate Diode – AEC-Q101、Dual Common Source - AEC Q101,VDS最大值(V):15~350V;VGS最大值(V):5.75~7V

|

产品型号

|

品类

|

Configuration

|

VDSmax(V)

|

VGSmax(V)

|

Max RDS(on) (mΩ)

@ 5 VGS

|

QG typ(nC)

|

QGS typ (nC)

|

QGD typ (nC)

|

QOSS typ (nC)

|

QRR(nC)

|

CISS (pF)

|

COSS (pF)

|

CRSS (pF)

|

ID(A)

|

Pulsed ID (A)

|

Max TJ (°C)

|

Package(mm)

|

Launch Date

|

|

EPC2040

|

Enhancement Mode Power Transistor

|

Single

|

15

|

6

|

30

|

0.745

|

0.23

|

0.14

|

0.42

|

0

|

86

|

67

|

20

|

3.4

|

28

|

150

|

BGA 0.85 x 1.2

|

Apr, 2017

|

选型表 - EPC 立即选型

BRC Solar Selects EPC 100V eGaN FETs for Next Generation Solar Optimizer

Designing EPC‘s EPC2218 100V FETs into BRC Solar GmbH‘s next generation M500/14 power optimizer has enabled a higher current density due to the low power dissipation and the small size of the GaN FET making the critical load circuit more compact.

【应用】eGaN FET EPC2051助力激光雷达发射端高功率纳秒级别脉冲设计

在激光雷达的发射链路中,为实现雷达高分辨率的设计,需产生高功率、纳秒级别的激光脉冲。要达到这样的设计要求,普通MOS不能满足要求,需要采用GaN 搭配高功率Laser器件进行实现。EPC2051是EPC公司生产的氮化镓场效应晶体管(eGaN FET),已经成功的应用在激光雷达上。

【应用】采用eGaN FET EPC2045实现低成本高性能的DCDC设计

EPC2045是一款100V/7mΩ、电流能力高达16A的增强型氮化镓场效应晶体管。目前采用EPC2045的EPC9130的功率密度做到了1250W/in³,在成本上可以实现¥0.5/W以内的低成本设计。EPC2045相比于Si MOSFET,在损耗上优势也比较明显。在48V输入、12V/10A输出、驱动频率为500KHz的条件下,EPC2045可提供1.5%的更高效率。

EPC2057氮化镓场效应晶体管材料成分声明

本资料为EPC2057元器件的材料成分声明,由Efficient Power Conversion (EPC)公司于2024年7月8日发布。声明中详细列出了该元器件的各组成部分及其所含物质,包括硅、氧化硅、氮化硅、氮化镓、铝、氮化铝、钛、氮化钛、铜、钨、聚酰亚胺等,并提供了每种物质的CAS编号、重量百分比和总重量。声明强调,所提供的数据为估算值,可能因技术要求和开发而变化,EPC可能随时更新此文件,且声明可能不包括最终产品中电气设备内掺杂剂和金属材料的微量信息。

EPC - EGAN FET,氮化镓场效应晶体管,EPC2057

【产品】EPC新型200V eGaN FET的性能相比传统Si MOSFET提高了一倍

EPC推出新型200V eGaN FETs(氮化镓增强型功率晶体管),相比于传统的硅功率MOSFET的性能提高了一倍。新第五代设备的尺寸仅为上一代产品的一半,栅电极和源电极之间的距离有所减小,金属层的厚度增加等诸多改进使第五代FET的性能提高了一倍。

EPC2934C氮化镓场效应晶体管材料成分声明

本资料为EPC2934C元器件的材料成分声明,由Efficient Power Conversion (EPC)公司于2024年5月6日发布。声明中详细列出了该元器件的各组成部分及其所含物质,包括硅、氮化镓、铝、钛、铜、钨、聚酰亚胺等,并提供了每种物质的CAS编号、重量百分比和总重量。声明强调,所提供的数据为估算值,可能因技术要求和开发而变化,EPC可能随时更新此文件,且声明可能不包括最终产品中电气设备内掺杂剂和金属材料的微量信息。

EPC - EGAN FET,氮化镓场效应晶体管,EPC2934C

【应用】基于eGaN FET与 GaN IC的低成本ToF激光雷达方案

用于激光雷达系统的典型脉冲激光驱动器通常使用与激光器和电源串联的半导体功率开关器件,其性能受寄生电感和半导体功率器件的速度所限制。GaN技术则能够支持短距离和远距离激光雷达传感器的设计。EPC公司的EPC9126和EPC9126HC是针对远距离直接飞行时间应用的大电流激光二极管驱动器的演示系统,EPC9144激光驱动器演示系统针对间接飞行时间应用进行了优化。

【产品】EPC新推3mΩ/40V的eGaN FET,适合USB-C电池充电器、超薄型负载点转换器

2020年12月,增强型硅基氮化镓(eGaN)功率场效应晶体管和集成电路的全球领先供应商宜普电源转换公司(EPC),推出了3mΩ/40V的EPC2055增强型氮化镓场效应晶体管(eGaN FET),以提高现有低压氮化镓晶体管的产品性能。

EPC 29215_55氮化镓场效应晶体管材料成分声明

本资料为EPC29215\_55型号元器件的材料成分声明。声明中详细列出了芯片的构成元素、相应物质、CAS编号、重量百分比和总重量。声明指出,所提供的数据为近似值,基于工程计算,可能因技术要求和开发而随时更改。EPC可能不通知即更新此文件。声明可能不包括最终产品中电气设备内掺杂剂和金属材料的微量信息。

EPC - EGAN FET,氮化镓场效应晶体管,EPC29215_55

【专题】硅MOS的终结者——氮化镓eGaN FET

相比先进的硅基器件,当今商用化的氮化镓场效应晶体管(eGaN FET)及集成电路的性能高出5至50倍。

【应用】eGaN FET EPC2212助力车载激光雷达设计,Qg仅3.2nC

EPC生产的eGaN FET EPC2212为满足车规AEC-Q101标准的产品,已经成功应用在车载激光雷达设计上。相对于Si MOSFET,氮化镓优势在于开关延时短,响应速度更快,同样的电压下,冲击电流更大。EPC2212耐压100V,瞬态电流高达75A(Tpluse=300μS),Qg低至3.2nC。

电子商城

服务

提供语音芯片、MP3芯片、录音芯片、音频蓝牙芯片等IC定制,语音时长:40秒~3小时(外挂flash),可以外挂TF卡或U盘扩容。

最小起订量: 1pcs 提交需求>

世强深圳实验室提供Robei EDA软件免费使用服务,与VCS、NC-Verilog、Modelsim等EDA工具无缝衔接,将IC设计高度抽象化,并精简到三个基本元素:模块、引脚、连接线,自动生成代码。点击预约,支持到场/视频直播使用,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论