【应用】工作频率最高达2GHz的瑞萨时钟芯片8SLVD1204为网络通信处理板提供高速可靠时钟信号

现代的高性能处理器为了适应各种复杂的应用场合,集成了越来越多的功能和接口。比如PCIe,USB3.0,SATA,SGMII等等,随着接口速率的提高,处理器对时钟品质的要求也越来越高。瑞萨电子的8SLVD1204是一款双输入,四扇出的时钟芯片,工作频率最高达2GHz。本文介绍了它在一款网络通信处理板卡上的设计应用。

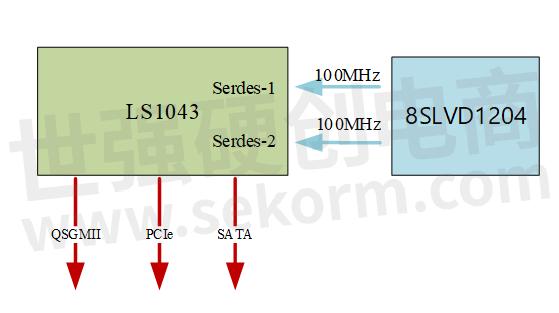

该项目是一块基于PowerPC架构处理器的网络通信处理板,CPU为NXP的LS1043,CPU具有两组支持多协议的Serdes接口,可以根据需要配置为PCIe、QSGMII、SATA、SGMII等通信接口,单通道Serdes最高速率可以达到5Gbps。这也要求外部提供两组100MHz的差分时钟,经过内部PLL倍频后分配给不同的接口使用。IDT(被RENESAS收购)公司的8SLVD1204具有2组差分输入和4组差分输出,正好可以满足该需求。

其Serdes部分的时钟框图如下所示。

图 1 处理器Serdes接口时钟框图

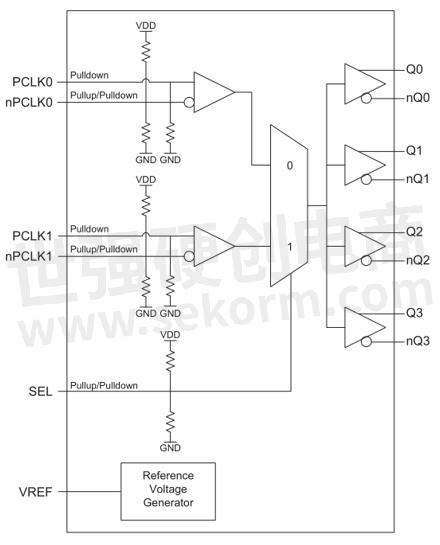

8SLVD1204的功能框图如下图所示。

图 2 8SLVD1204内部功能框图

8SLVD1204主要参数如下表所示。

从上表可以看出,8SLVD1204具有优秀的性能,很低的相位抖动和输出偏移,以及传输延迟等。采用单一3.3V供电,可以简化电源设计,而且体积只有3mmx3mm,在pcb上占用的面积几乎可以忽略不计。

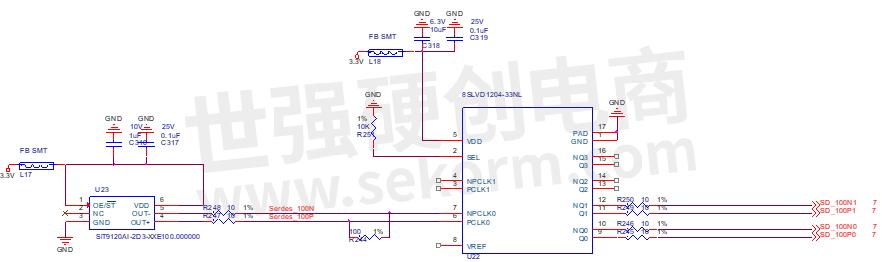

8SLVD1204的电路图如下所示。

图 3 8SLVD1204原理图

8SLVD1204的输入可以采用单端输入,也可以采用差分输入,这里采用了LVDS的差分晶振作为时钟输入,电路更简洁,抗干扰性能也更好。在8SLVD1204的时钟输入端需要加一颗100欧姆的电阻作为终端匹配。8SLVD1204的电源并不需要做特别的处理,只需要用磁珠和电容做成一个简单的LC滤波即可。因为8SLVD1204有两组输入信号,这里时钟信号从CLK0输入,所以SEL引脚做接地处理。8SLVD1204的输出有4组,而LS1043处理器的Serdes需要两组100MHz差分时钟信号,所以这里只用了其中2组,剩下2组留空不用。VREF引脚为LVPECL时钟输入作为参考电压用,这里的输入为LVDS,所以也留空不用。整个电路既简单也很简洁。

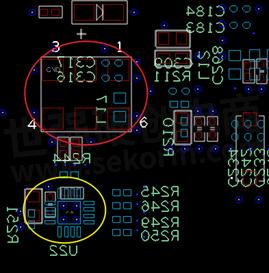

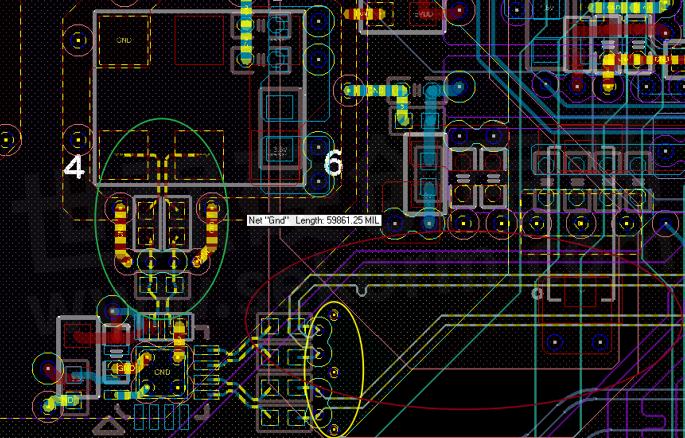

8SLVD1204的PCB布局图如下所示。

图 4 8SLVD1204 PCB布局图

图中红色圈内为100MHz差分晶振,下方黄色圈内为8SLVD1204。器件布局时差分晶振尽量靠近8SLVD1204放置,以减少外界耦合进来的干扰,其他不相关的器件则距离8SLVD1204稍微远一些,减少100MHz时钟造成的干扰。这里100MHz差分晶振放在正面,而8SLVD1204放在背面,主要是为了避免输出时钟走线交叉。

下图是8SLVD1204的走线图。

图 5 8SLVD1204走线图

图中绿色圈内为8SLVD1204的输入信号,红色圈内为8SLVD1204的输出信号,因为都是差分信号,所以都按照差分信号的布线规则紧靠在一起走线,并且做了等长50mil的处理,避免其他走线对差分信号产生干扰。此外在黄色圈内靠近输出信号的过孔处还添加了接地孔,用于减小差分信号换层时的回流路径,可以改善时钟信号完整性。

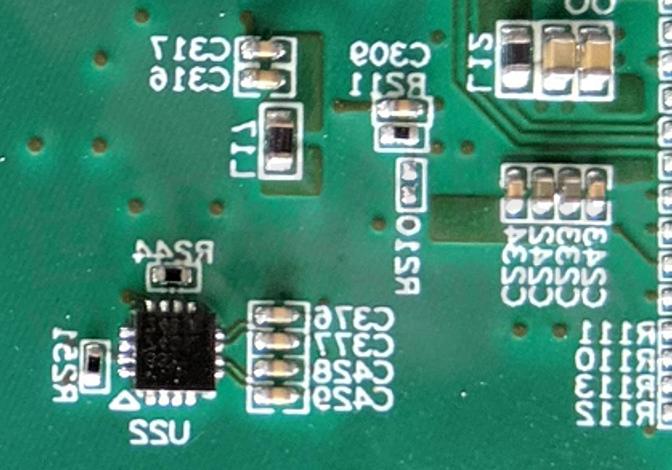

8SLVD1204电路实物图如下所示。100MHz差分晶振因为放在另外一面,所以图中并没有显示。

图 6 8SLVD1204板卡实物图

实际测试,处理器LS1043的Serdes接口采用8SLVD1204提供的100MHz时钟信号,采用8SLVD1204提供的时钟,经过长时间测试,不论时PCIe接口、QSGMII接口还是SATA接口都表现出了稳定和可靠的性能和速度,获得客户的充分认可。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由深蓝的鱼提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【成功案例】Renesas提供时钟芯片产品组合为英特尔®凌动™处理器的嵌入式系统提供方案

英特尔®凌动™处理器使移动设备的启动速度快、工作时间长,同时还支持超高清4K多媒体和高帧率 (FPS) 流处理。这些处理器主要用于嵌入式和工业应用,如通信设备,工业控制,车载信息娱乐系统(IVI)和自动化。而IDT 提供业界最丰富、最全面的芯片时钟产品组合,其拥有业界最全面支持凌动™处理器的时钟解决方案,可为基于凌动™处理器的所有应用提供时钟解决方案。

【应用】具有两个可编程时钟报警和一个可编程方波输出实时时钟IC助力汽车仪表盘应用

本文推荐的是由IDT(瑞萨收购)推出的一款IDT1337AG实时时钟芯片。首先,该款实时时钟芯片是超低功耗的串行实时时钟(RTC)器件,具有两个可编程时钟报警和一个可编程方波输出。地址和数据可通过I2C总线串行传输,数据接口协议标准,具有出色的可扩展性和集成性,便于汽车仪表盘主控访问,简化设计电路,降低设计难度。

【成功案例】小型化封装时钟芯片8T49N286成功应用在femto基站,极大的简化了设计

IDT(Renesas收购)的一款时钟芯片8T49N286,具备小型化封装,4路输入,8路输出,两级锁相环,小数分频,出厂固化配置可选等等功能极大了简化了设计,也丰富了系统的扩展。完全满足Femto基站在有限空间里的复杂的时钟需求。

E1接口LIU芯片,除了IDT的82V2082等,还有其它厂家生产类似芯片吗?国内有没有类似产品?

1、世强是IDT(艾迪悌)的官方授权一级代理商,代理IDT(艾迪悌)旗下时钟,电源管理IC,传感器等产品,库存丰富,正品保证。用户可以查询获取来自IDT(艾迪悌)的最新产品和技术资讯、官方资料库,以低于行业的价格,购买IDT(艾迪悌)最新产品,享受供货保障。详见链接:模拟混合信号产品的领导者——IDT(艾迪悌)。2、可在“世强元件”官网搜索“E1接口”“LIU”等关键字获得更多信息和产品。

在500mW的一体化站的基带部分需要一个1588的时钟芯片, 请帮推荐。

推荐世强代理的IDT的 8A34005可以满足。 收据手册链接:https://www.sekorm.com/product/721435.html

【经验】解析Renesas时钟发生器通过软件查看PLL锁定状态的方法

Renesas时钟发生器5P49V6965A000NLGI是可编程时钟发生器,相位抖动低至0.5ps,支持单端输出1kHz~200MHz,差分格式输出频点1kHz~350MHz,广泛应用于基站、数据中心等应用中。本文解析通过软件查看PLL锁定状态的方法。

大咖座谈 | 半导体行业对AI在终端场景及应用中的推动

尽管关于生成式AI和ChatGPT-4的讨论不绝于耳,但到2025年,大约75%的数据将来自网络边缘设备,而非云端。与此同时,目前企业收集的数据有90%被丢弃,这也为我们带来一个激动人心的机会,来寻找这些数据的有效用途。

替代8V19N474抖动衰减器时钟芯片的SI5395,无缝切换仅0.5ns瞬态相位变化

Silicon Labs最新推出的基于第四代DSPLL技术的抖动衰减器时钟芯片SI5395,主要用于OTN、56G/112G PAM4 SerDes、100/200/400 GbE 同步以太网等设备中的时钟链路设计。本文通过IDT 8V19N474与SI5395对比,确定SI5395可做备选方案,并提供5种时钟域,更低的通信误码率,不需要额外的分离VCXO、LPF等器件组成外部衰减PLL,

瑞萨RL78芯片休眠时时钟怎么配置才可以保证功耗最低?

瑞萨RL78系列MCU在STOP模式下,高速系统时钟振荡器和高速片上振荡器停止工作,并停止整个系统,可以大幅降低CPU的工作电流;在进入STOP模式之前,需要设定定时器唤醒时间和检测电压窗口范围,进入STOP模式后,定时器会定时进入SNOOZE模式,进入该模式后,会通过ADC检测输入的电压值,如不在预先设定的范围内,则返回STOP模式,等待下次唤醒;如在设定的范围内,则会唤醒CPU,进入运行模式。在此情况下可实现最低功耗,时钟频率越低功耗越低。需要注意 在使用外部时钟时,在SNOOZE模式下ADC不能工作,需要切换回内部高速时钟,切换后ADC工作正常。

通信模块上面想找一颗国产的时钟芯片,要求不低于4路输出的单端buffer,抖动不能高于55fs,3.3V的供电电压,2×2 mm DFN封装

推荐奥拉的AU5424BG-DNR,可功能替代瑞萨的5PB1102CMGI,具有低于50fs的附加抖动,点入电压范围在1.8V-3.3V之间,4路输出,支持同步无故障输出启用(OE)功能 具体参数可参考数据手册:https://www.sekorm.com/doc/3656803.html

R5F10BBF芯片的内部时钟频率是多少,其精度是多少?

瑞萨RL78系列MCU芯片R5F10BBF内部支持1~64MHZ的内部高速时钟,在全工作温度范围内保持±2%的精度,可对内部高速时钟进行微调。

瑞萨RH850系列芯片,上电时间到main函数执行时间较长,应该如何优化呢?

可以RH850的启动文件cstart.asm中,执行时钟初始化函数,将时钟倍频到80M,时钟初始化函数在asm文件中的调用例子如下 .extern R_CGC_Create jarl _R_CGC_Create,lp

瑞萨的型号为RC21012A001GNA的时钟芯片需要根据配置文件输出一个eeprom烧写程序,还请技术支持帮忙输出一下,配置文件是现成的。

您好,可以通过以下步骤导出烧写文件

瑞萨R7F702300EABA芯片如何配置打开TAUD模块的时钟?

瑞萨RH850/U2A芯片的MSR_TAUD是被保护的寄存器,因此,为了打开TAUD时钟,我们需要执行以下代码: SYSCTRL.MSRKCPROT.UINT32 = 0xA5A5A501UL;//KCPROT_ENABLE; SYSCTRL.MSR_TAUD.UINT32 =0x00; SYSCTRL.MSRKCPROT.UINT32 = 0xA5A5A500UL;//KCPROT_DISABLE;

【产品】LVDS扇出缓冲芯片IDT8SLVD1204I,时钟分配应用的理想选择

IDT8SLVD1204I是IDT(Renesas收购)推出的一款高性能差分LVDS时钟扇出缓冲器。该芯片专为高频、极低附加相位噪声时钟和数据信号的扇出而设计。IDT8SLVD1204I的特点是采用2.5V电源供电,保证出色的输出至输出偏斜特性,这使得IDT8SLVD1204I成为那些有明确性能要求的和可重复性的时钟分配应用的理想选择。

电子商城

现货市场

服务

Ignion可支持多协议、宽频段的物联网天线方案设计,协议:Wi-Fi、Bluetooth、UWB、Lora、Zigbee、2G、3G、4G、5G、CBRS、GNSS、GSM、LTE-M、NB-IoT等,频段范围:400MHz~10600MHz。

最小起订量: 2500 提交需求>

提供语音芯片、MP3芯片、录音芯片、音频蓝牙芯片等IC定制,语音时长:40秒~3小时(外挂flash),可以外挂TF卡或U盘扩容。

最小起订量: 1pcs 提交需求>

登录 | 立即注册

提交评论