【经验】先楫HPM6000系列双核MCU的使用和操作方法

多核的微控制器(MCU)向来是设计上的一大挑战,尤其是多核异构的设计。而MCU双核作为其中的精简版本,凭借其超强的处理性能和便捷开发的特性,很快受到业界的好评。先楫半导体先后推出了几款高性能MCU双核产品,集成2个RISC-V处理器,其中HPM6700系列两个核的最高主频都可以达到816MHz。本文通过对先楫HPM6000系列双核的使用方法、工程编译与调试、双核通信方式和资源分配等内容的介绍,全方位给大家介绍双核的使用和操作,让大家轻松玩转双核,完成更多的片上系统功能开发。

接下来,让我们看一看HPM6000系列双核MCU是如何玩转起来的吧。

双核简介

HPM6000系列的双核配置,均集成2个RISC-V处理器,双核采用主从结构。CPU0和CPU1采用相同配置,如下:

●支持相同指令集

●相同容量的L1指令和数据缓存

32KB L1 I-Cache,4-way,128x64B cache line per way

32KB L1 D-cache,4-way,128x64B cache line per way

●相同容量的指令和数据本地存储器:256 KB ILM和256 KB DLM

CPU0和CPU1采用相同的存储器映射,以下为例外:

●CPU自身的指令/数据本地存储器ILM/DLM为私有;

●FGPIO为私有

●平台中断控制器PLIC为私有

●软件中断控制器PLICSW为私有

●机器定时器MCHTMR为私有

双核的三种使用方法推荐

不论是在RAM中运行,还是片上Flash运行,双核固件均是存储在Flash上。客户根据应用场景,选择在上电后将双核各自的镜像从Flash中装载到RAM中执行或者基于Flash片上执行。

根据应用场景,选择合适的运行方式,推荐以下几种:

方案一:Core0加载到RAM运行,Core1加载到RAM运行

RAM区域可以是各自的ILM,也可以片上的SRAM,或者是SDRAM。当然,装载CODE的RAM区域各自都是独立的。此方案应用与双核固件均占用小,可完全装载到RAM中运行。

固件存储位置:Core0和Core1的固件均存放在Flash指定区域(Flash分区规划)。上电后,BootRom从指定Flash区域装载Core0镜像到指定RAM运行(type:debug/release),Core0运行后从指定Flash 区域装载Core1镜像到指定RAM,然后运行Core1。

方案二:Core0基于flash xip(flash片上执行)运行,Core1加载到RAM运行

此方案应用与Core0核固件占用大, Core1核固件占用小。通常将Core0用来做应用复杂交互,Core1用来做高实时性,高性能的触发逻辑。

固件存储位置:

1. Core0和Core1的固件各自存放在Flash的指定区域(Flash分区规划)。

●优点:Core0和Core1可单独OTA。

●缺点:需要维护两个固件BIN文件,并存放到各自的区域中。

2. Core1的固件以数组(只读区)镜像的方式存储在Core0的固件中,Core0固件存放在Flash指定区域;官方例程中使用此方案。

●优点: 只维护一个固件。

●缺点:Core0和Core1不可单独OTA。

方案三:Core0基于flash xip0(flash片上执行)运行,Core1基于flash xip1(flash片上执行)运行

此方案应用与Core0核和Core1核固件均很大,双核均无法满足放到RAM中运行。

注意:由于双核均基于flash片上执行,如果使用同一个flash

XPI,会出现并发访问Flash的情况导致未知异常发生;如果强制顺序访问,访问效率极低,严重拖垮CPU运行速率;故不建议两个核使用同一个flash

XPI片上执行。建议使用XPI0和XPI1各自外挂一个FLASH,分别用于Core0 Flash xip0和Core1 Flash xip1。

固件存储位置:Core0和Core1的固件存储在各自外挂的Flash的指定区域中。

双核工程编译与调试

HPM双核是集成了两个RISC-V 处理器,是两个完全独立的CPU,故HPM双核工程是Core0工程和Core1工程两个独立的工程。因此HPM双核工程编译,其实是两个独立的单核工程的编译。用户只需要建立core0和core1的各自工程编译调试即可。

由于HPM-SDK例程中使用的是方案二,且Core1的固件以数组(只读区)镜像的方式存储在Core0的固件中,导致Core1工程为Core0工程的关联工程。因此在构建工程时,必须先构建生成Core0工程,作为关联工程Core1工程会自动生成。由于Core1的固件是Core0工程中的只读数组,故必须先编译Core1工程生成只读数组镜像后,再编译Core0工程。

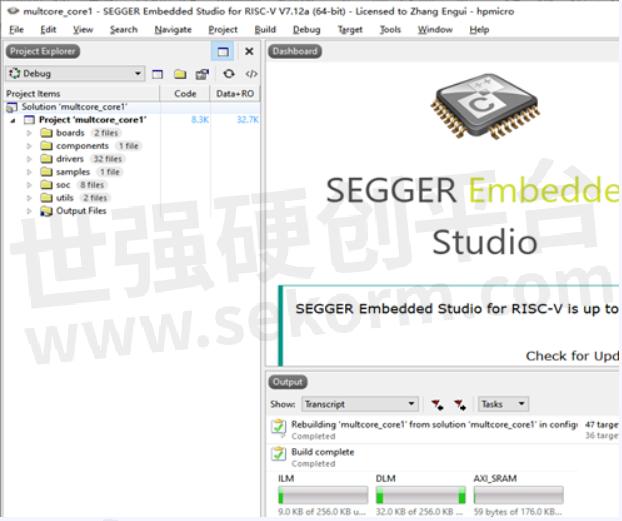

如下构建编译调试双核hello world工程:

A. 构建工程

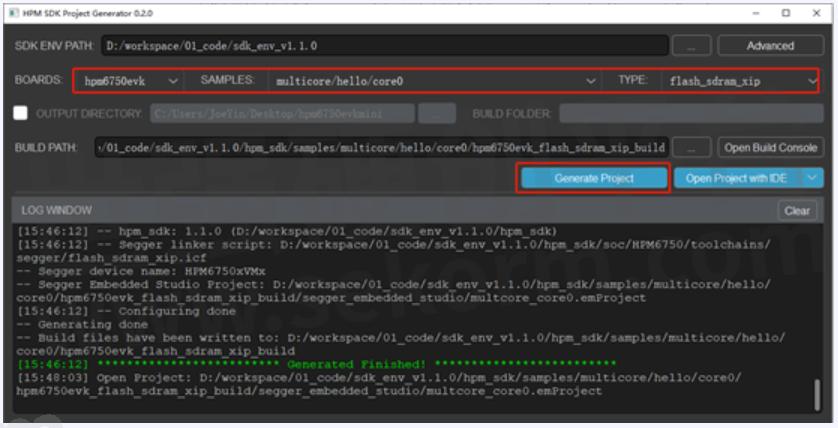

先构建生成Core0工程:

由于Core0是flash片上执行,故type选择:flash_sdram_xip或flash_xip

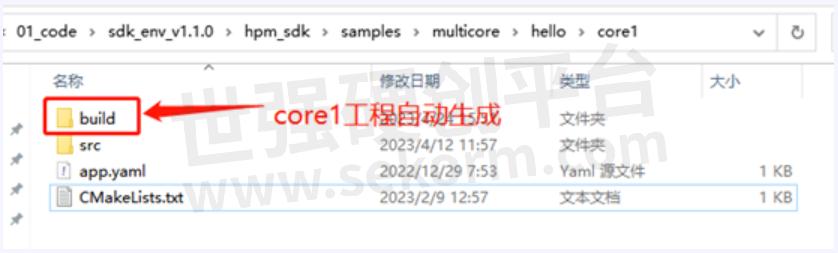

作为关联工程Core1工程会自动生成:

B. 编译工程

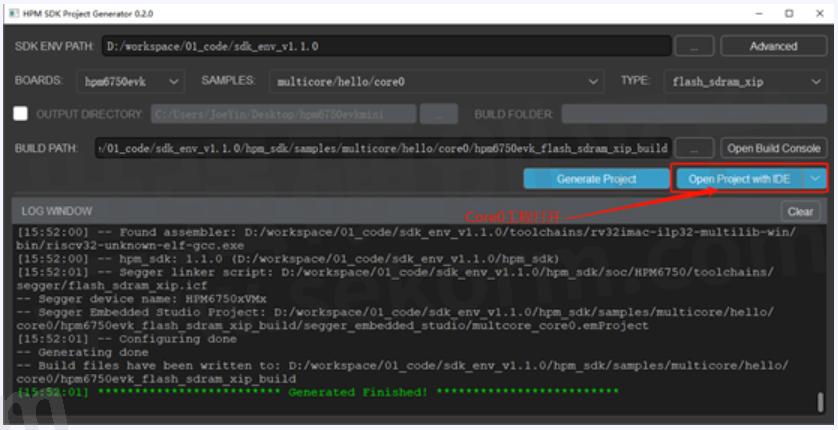

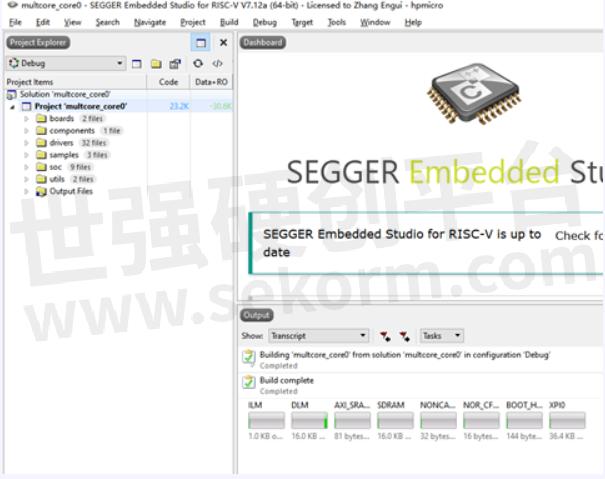

打开各自的工程(Core0通过GUI工具直接点击Open Project with IDE, Core1对应目录下双击打开工程)。

用SES编译各自的工程即可。

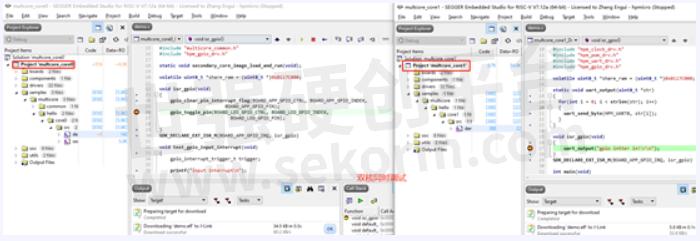

C. 工程调试

一、双核同时调试

基于OpenOCD调试(FT2232/DAP-LINK等)。

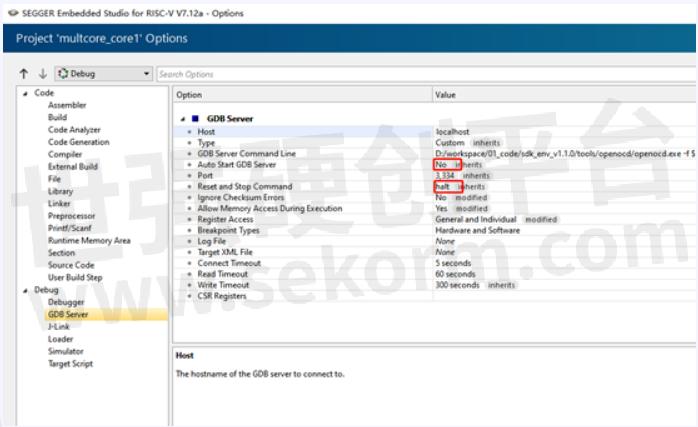

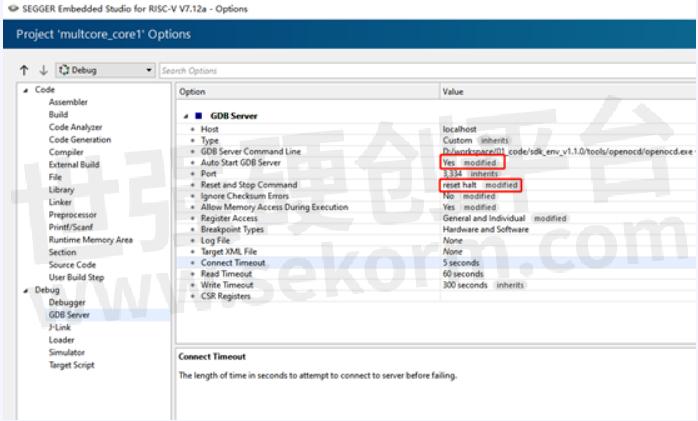

为了达到Core0和Core1同时调试,基于OpenOCD调试在HPM-SDK例程中,对Core1的Debug做了如下限制:

1)Core1不启动GDB Server,连接Core0启动的GDB Server。当然使用不同的port来区分是Core0(Port:3333)还是Core1(Port:3334)。

2)Reset和Stop时,直接hart停止运行。

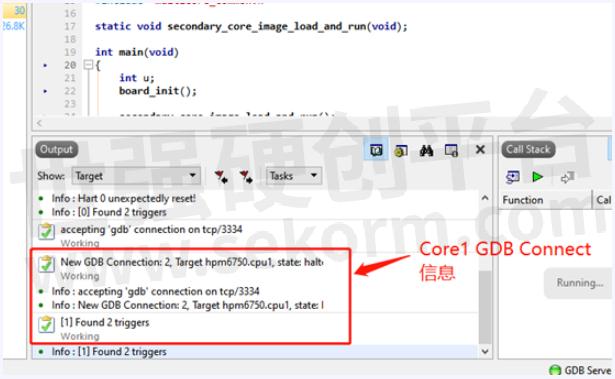

如下图:

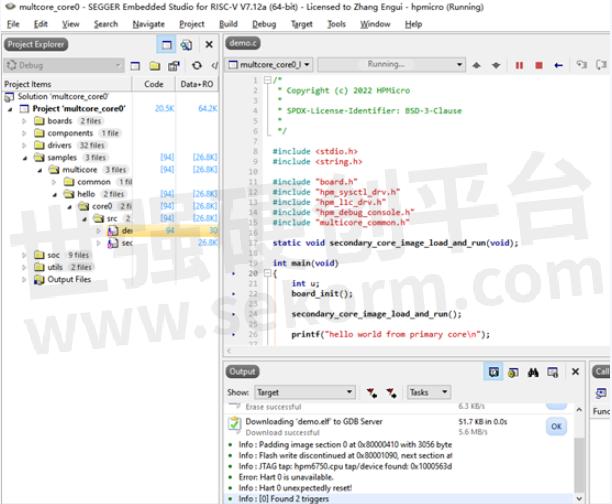

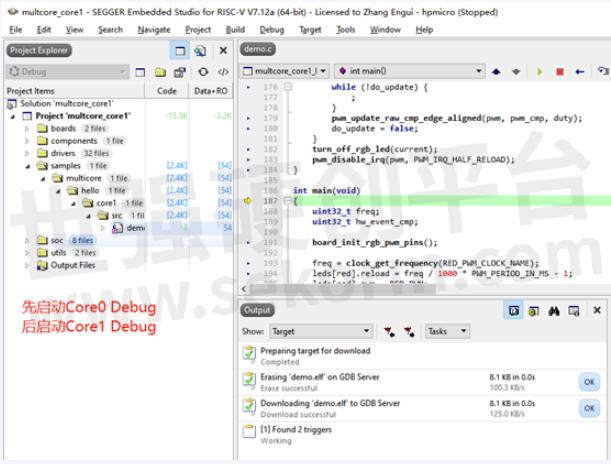

因此,调试HPM-SDK双核例程,步骤如下:

步骤1:Core0的工程调试,和正常的单核调试相同,正常SES启动debug即可。

步骤2:Core1的工程调试,由于上述限制(为了双核同时调试),必须先将Core0的工程Debug运行,然后在启动Core1的Debug仿真。

可在Core0 SES终端看到Core1 GDB connect信息:

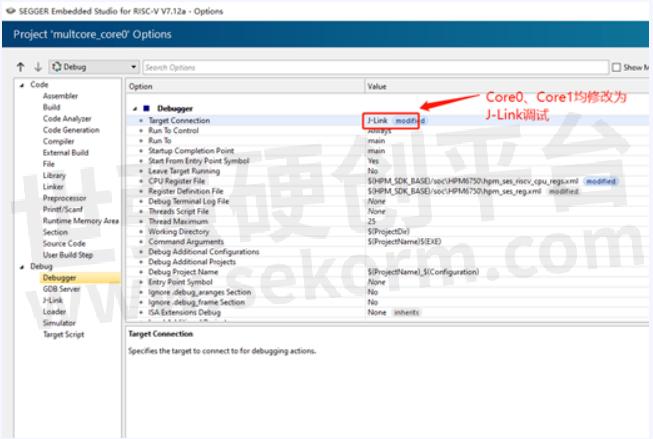

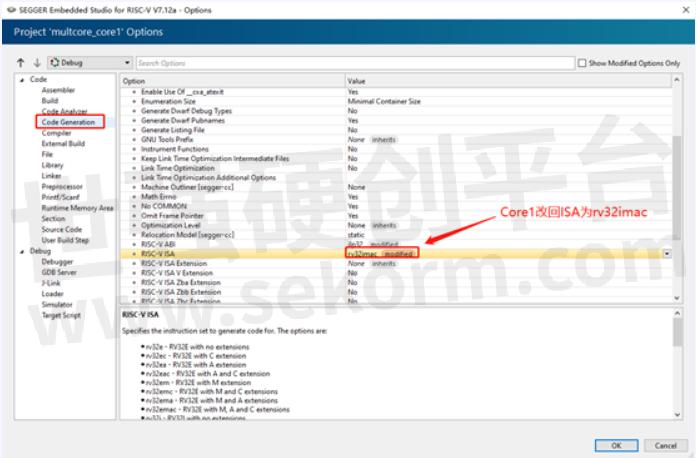

基于Jlink调试

基于Jlink调试,对Core0和Core1的Debug做如下修改:

1. Core0修改Debug连接target为:J-Link

2. Core1修改Debug连接target为:J-Link

3. Core1修改Debug Device为:HPM6750xVMx_CPU1

4. 由于SES修改Device为CPU1(上一步骤修改),联动修改ISA为:rv32i,导致编译等异常。故在Code Generation下改回ISA为:rv32imac。

5. 通常初始化时钟等外设在Core0中完成,故为了双核能同时调试,需先运行Core0 Debug至完成时钟等外设初始化后,方可Core1 Debug运行。

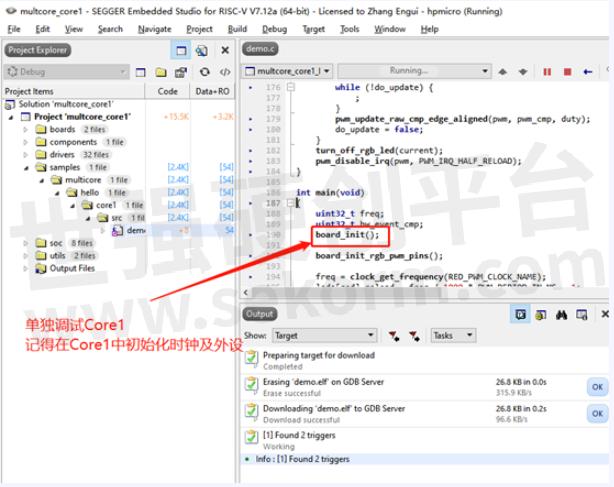

二、双核单独调试

基于OpenOCD调试

如果只用来单独调试Core1(Core0的单独调试不做任何修改即可),可修改Core1的Debug配置,如下:

Auto Start GDB Server: Yes

Reset and Stop Command: reset halt

修改后, 可直接启动Core1 Debug运行。

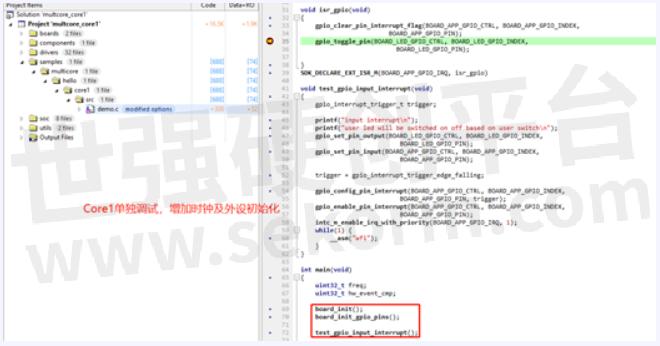

注意:由于CPU0,CPU1主从架构,通常外设等时钟初始化会在Core0中完成。如果是单独调试Core1,为了确保程序能正常运行,需在Core1工程中初始化时钟等外设。如下:

基于 Jlink 调试

单独调试Core1(Core0的单独调试不做任何修改即可),JLink修改同双核JLink修改一致(可参考上方介绍的内容)。

同样为了确保Core1能正常运行,需在Core1工程中初始化时钟等外设。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由玉鹤甘茗转载自先楫半导体HPMicro公众号,原文标题为:玩转MCU双核(上) 先楫HPM6000系列双核怎么玩?答案超乎你想象!,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

先楫半导体HPM APPS v1.7.0上线啦!

先楫半导体发布了HPM APPS v1.7.0,包含多项更新和新功能,如HPM双网口环网通信方案、Ethercat主站应用方案、I2S DMA CHAIN应用方案、hpm_monitor服务、SPI控制器操作Nor flash应用案例等。这些更新旨在提升微控制器性能,简化开发过程,并加速程序开发。

【经验】先楫半导体MCU HPM6750使用JLINK调试下如何进行串口打印配置

在使用JLINK调试先楫半导体HPM6750EVK2开发板调试时遇到不知如何使用SEGGER Embedded Studio (以下简称SES)内置的虚拟串口打印工具,本文介绍正确配置串口打印工具的步骤。

先楫半导体(HPMicro)HPM APPS v1.6.0上线啦!

HPM APPS是基于HPM SDK开发的上层应用软件开发套件。提供各种典型通用的应用解决方案,包含了中间件、组件、服务等,供用户使用评估。HPM APPS需搭配HPM SDK使用,且HPM APPS和HPM SDK版本一一对应。在参考方案时,建议先查阅文档开始。

国产高性能MCU又一力作,集成授权EtherCAT,助力工业伺服走向海内外

最近,先楫半导体发布中国首款拥有德国倍福公司正式授权EterhCAT从站控制器的高性能MCU产品HPM6E00系列,将国产高性能MCU在工业领域的应用推向新高度。

先楫半导体hpm_sdk v1.6.0全新上线!新增HPM6E80产品支持

先楫半导体hpm_sdk v1.6.0上线!新增HPM6E80产品支持。HPM6E00系列MCU是一款高性能、高实时以太互联,RISC-V双核微控制器。HPM6E00系列提供多达4端口千兆以太交换模块,支持TSN,并且支持3端口EtherCAT从站控制器,以及32路高分辨率PWM输出,高精度运动控制系统,可以在工业自动化领域实现基于高实时性,低延时以太网的高性能伺服电机控制,机器人运动控制等应用。

【IC】先楫半导体最新款高性能MCU HPM5301,搭载单核32位RISC-V处理器,主频高达360MHz

先楫半导体于2023年11月24日宣布推出高性能HPM5300系列MCU最新款——HPM5301芯片。这款MCU搭载单核32位RISC-V处理器,采用QFN48封装,是迄今为止先楫推出的最简单易用的产品。该芯片的开发板HPM5301EVKLite也同步上市。

媒体视角 | 先楫半导体HPM6E00系列MCU填补国内空白,EtherCAT中国首授权

2023年12月先楫半导体正式推出中国首款拥有德国倍福公司正式授权EtherCAT从站控制器的高性能MCU产品HPM6E00系列。先楫半导体HPM6E00系列产品采用国际流行的RISC-V架构,主频高达600MHz,有单双核选项,集成了德国倍福公司授权的EtherCAT从站控制器,具备高性能运动控制、高实时工业以太网互联的特性。

先楫HPM6000系列高性能MCU在Linux环境下自动生成SDK本地化工程

本文介绍先楫半导体HPM6000系列高性能MCU在Linux环境下自动生成SDK本地化工程,SDK下载地址可通过世强FAE获取并提供技术支持。工程支持世强整合的SekormStudio(eclipse+GCC)以及第三方Segger Studio集成开发环境。

【应用】基于RISC-V的高主频MCU HPM6750用于LED大屏,双千兆以太网透传实现实时控制

基于RISC-V的高主频MCU能让LED大屏显示系统实现更高的驱动频率及更高的实时性。HPM6750是先楫半导体开发的采用RISC-V 内核、具有高主频及创新总线架构的双核高性能MCU,能通过双千兆以太网透传的方案加双核加持完美解决高速的链路设计。

先楫半导体(HPMicro)HPM6000家族MCU选型指南

描述- 上海先楫是一家致力于高性能嵌入式解决方案的半导体公司,产品覆盖微控制器、微处理器和周边芯片,以及配套的开发工具和生态系统。 目前已经量产的两个高性能通用MCU产品系列HPM6700/6400及HPM6300,性能领先国际同类产品,并完成AEC-Q100认证,全力服务中国工业,汽车和消费市场。公司成立于2020年6月,总部坐落于上海市张江高科技园区,并在天津、深圳和南京均设立分公司。 核心团队来自世界知名半导体公司管理团队,具有15年以上,超过20个SoC的丰富的研发及管理经验。

型号- HPM6320IEP,HPM6454IAN,HPM6754IAN,HPM6450,HPM6750IAN,HPM6350,HPM6754IVM,HPM6300系列,HPM6450IAN,HPM6454IVM,HPM6750IVM,HPM6320IPA,HPM6000家族,HPM6360IPA,HPM6360IEP,HPM6364IPA,HPM6430IVM,HPM6300,HPM6400,HPM6320,HPM6364,HPM6364IEP,HPM6700,HPM6430IAN,HPM6350IPA,HPM6340,HPM6000,HPM6360,HPM6730IAN,HPM6340IEP,HPM6730IVM,HPM6350IEP,HPM6340IPA,HPM6700系列,HPM6450IVM,HPM6454,HPM6730,HPM6430,HPM6400系列,HPM6750,HPM6754

HPM6700/6400 系列高性能微控制器勘误表

型号- HPM6450IVMX,HPM64A0AVM2,HPM6730IVMX,HPM64G0CAN2,HPM6754IANX,HPM6454IANX,HPM6750IANX,HPM6700 系列,HPM6430IANX,HPM64G0CVM2,HPM66400,HPM6750IVMX,:HPM6750IVM2,HPM6430IVMX,HPM6454IVMX,HPM6450IANX,HPM64A0AAN2,HPM6730IANX,HPM6700,HPM66400 系列,HPM6754IVMX

【IC】有动静!先楫出了颗适用机器人的国内首款内嵌ESC高性能MCU——HPM6E00

先楫半导体(HPMicro)推出的新款MCU——HPM6E00,引发了外界的广泛关注。这家成立仅四年的公司,凭借“国内首款内嵌ESC的高性能MCU”,再次证明了其在MCU领域的创新实力。

【经验】MCU HPM6750使用ISP烧录程序步骤及注意事项

先楫半导体推出的HPM6750是一款高性能MCU,采用双RISC-V内核,主频可达816MHz,使用自主的创新总线架构、高效的L1缓存和本地存储器,高达9220CoreMark和高达4651 DMIPS的MCU性能纪录;同时整个MCU还整合了一系列高性能外设。

HPM6300 系列高性能微控制器勘误表

型号- HPM6330ICE2,HPM6360IDC2,HPM6364IPAX,HPM6360IEPX,HPM6340IPAX,HPM6364IPB2,HPM6350IEPX,HPM6320IPAX,HPM6360IPA2,HPM6350IPAX,HPM6320IEPX,HPM6364IDC2,HPM6360IPB2,HPM6300,HPM6340IEPX,HPM6364IEPX,HPM6300 系列,HPM6360IPAX

电子商城

现货市场

服务

拥有中等规模的SMT、DIP以及成品组装产线;支持PCBA及成品OEM/ODM代工组装制造;在嵌入式系统、物联网系统等具备专业性量产制造的项目组织和服务能力。

提交需求>

支持 3Hz ~ 26.5GHz射频信号中心频率测试;9kHz ~ 3GHz频率范围内Wi-SUN、lora、zigbee、ble和Sub-G 灵敏度测量与测试,天线阻抗测量与匹配电路调试服务。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳/苏州 提交需求>

登录 | 立即注册

提交评论