【应用】芯科科技提供基于Xilinx 处理器+Si5388/9时钟芯片的IEEE1588整体解决方案,助力5G开发

当前,随着5G在中国越来越热,5G的开发项目也多了起来,为了满足5G网络对每个节点更高的时钟同步要求,IEEE1588时钟协议也成为了5G网络上各个节点的必备需求。去年下半年,SILICON LABS推出了自己的基于Xilinx 处理器(1588 stack)加Silicon Labs的 Si5388/9(servo)的1588的整体解决方案。

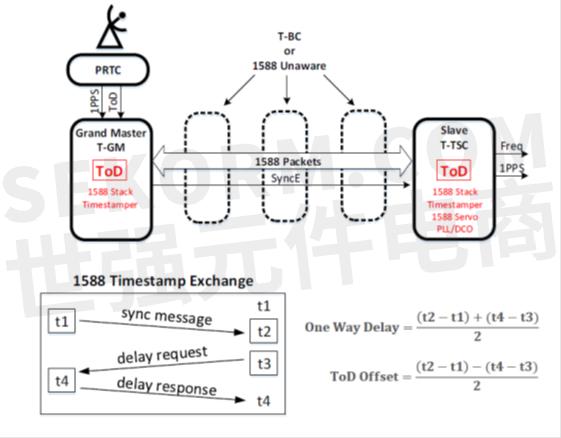

在对Silicon Labs的IEEE1588的整体解决方案作介绍之前,先简单的给大家说一下1588协议的目的:

1. 实现主从节点之间ToD(Time of Day)的同步

2. 在从节点,通过ToD信息,来调整从节点的时钟频率和相位,使之尽可能与主节点时钟保持一致

Table1:1588协议实现简图

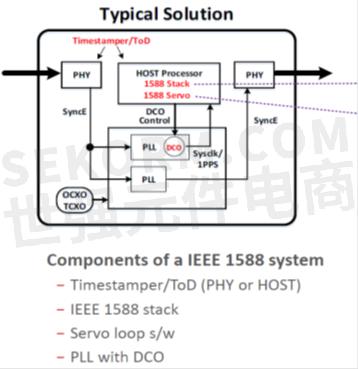

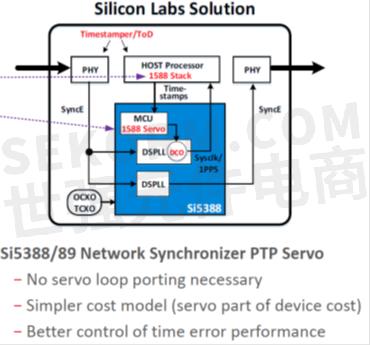

从以上的工作简图,在5G网络每个节点,都会需要一个1588模块。而从节点比主节点会有更多的时钟调节的需求。 在现在通常的1588方案中,ToD信息的处理是有模块处理器来完成的,处理器再根据ToD的处理结果来对时钟芯片进行频率和相位的调节。而在Silicon Labs的 1588方案中,我们把对时钟的频率和相位的调节功能下放到我们的时钟芯片-Si5388. 这样大大简化了对主处理器的资源的占用。

Table2. 典型1588从节点的解决方案

Table3. Silicon Labs 1588解决方案

在Silicon Labs的整体解决方案中,Silicon Labs把自己的Servo部分控制协议固化到自己的Si5388芯片中,同时借用了Xilinx的FPGA来运行自己的ToD部分的处理协议。通过这样简单的双芯片方案来为客户提供一个整体的1588解决方案。为了满足不同客户的不同需求,Silicon Labs现在还在做进一步开发,把我们的ToD部分的处理协议移植到更多的主处理器上,如NXP基于ARM核的CPU。当然,客户也可以购买我们的1588软件协议,自行移植到自己的ARM处理器上。

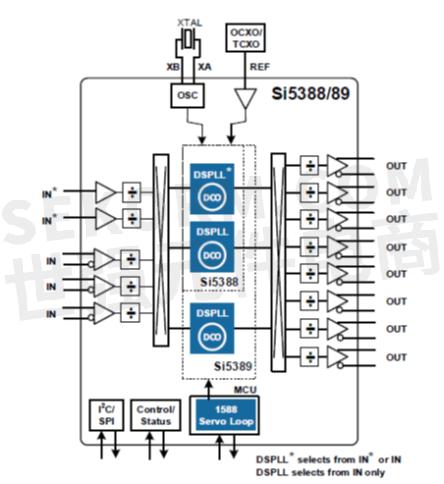

以下对Silicon Labs最新推出的Si5388做个简单的介绍:

Tablet4. Si5388/9功能简图

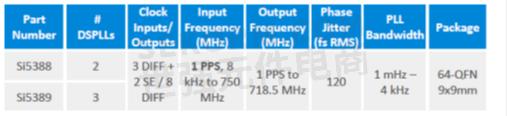

Tablet5. Si5388/9性能表

Si5388 的基本性能:

1. 3路差分输入,2路CMOS输入,可以支持1Hz GPS CMOS输入

2. 7路差分输出,每差分输出可以用作2CMOS输出,支持1Hz CMOS输出

3. 内置MCU,用于IEEE1588 servo 协议调控

4. 3路独立的PLL,可输出任意频率时钟

5. 每个输出附带DCO频率调节,调节精度可到1ppt

6. 附带去抖功能,输出抖动可达120fs RMS (12K-20M 范围)

7. 支持输入无缝切换功能

8. 芯片支持预配置功能

9. 支持XO,TCXO/OCXO双参考时钟,同时满足去抖和1588时钟对漂移的要求

10. 支持LOL,LOS, OOF报警功能

11. 可编程支持多种时钟输出格式:LVPECL,LVDS,HSCL,LVCMOS

12. 支持规范:G.8262, G.8262.1, G.8273(Class A/B/C), G.812, G.813

13. 支持T-BC 和 T-TSC 模式

如果客户已经拥有自己的1588协议,Silicon Labs也可以直接提供对应的时钟芯片Si5383,它是Si5388去掉MCU和1588 Servo协议的简化版芯片。客户可以直接通过SPI/I2C接口来控制Si5383的DCO进行时钟调节,调节精度一样可以最大达到1ppt。

- |

- +1 赞 0

- 收藏

- 评论 1

本文由宇宙无敌美少女转载自Silicon Labs,原文标题为:Silicon Labs时钟芯片在5G项目中应用,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

一个使用无线专用去抖时钟芯片Si5386配置JESD204B接口时钟延时的应用案例

Silicon Labs公司的无线专用去抖时钟芯片Si5386集成DSPLL核心技术的JESD204B去抖时钟芯片,广泛用于无线基站设备中,用来消除由于离散的VCXO和环路滤波器组件带来的额外噪声。本案例就是一个实现4对延时调节功能JESD204B的DCLK/SYSREF配置的例子。

【应用】大普通信1588时钟芯片ACS9522用于5G小基站,内嵌包过滤算法,BMCA及时钟管理

本文推荐在小基站BBU和Rhub\pRRU传输数据时同步信号可采用大普通信推出的1588时钟芯片ACS9522,内嵌包过滤算法,BMCA及时钟管理;内嵌处理器,专门处理PTP;不受CPU负载及多任务处理影响;配合PTP功能或单独频率生成。

【应用】一种基于SI53301时钟芯片的光传输设备线卡应用方案

Silicon Labs时钟芯片SI53301相对的附加抖动仅为45fs,因此只要输入源(一般是XO)的抖动指标不高的话,不会引入过大的额外相位噪声。SI53301自带分频功能,在某种程度上可以代替实现PLL的部分功能,SI53301支持2分频和4分频,有两个输出Bank,每个Bank分别对应DIVA和DIVB分频器。

一款适合IEEE 1588V2的专用时钟芯片

Silicon Labs日前推出了专门实现IEEE 1588协议的超低抖动时钟芯片SI5348,这款芯片可以满足IEEE 1588 V2组网对系统时钟极其苛刻的指标要求,完美实现IEEE 1588 V2协议。

【产品】奥拉AU561x去抖时钟芯片:提供开创性的精度和同步性能,是5G通信优选时钟解决方案

奥拉半导体凭借其第三代去抖时钟芯片产品系列站在了时钟芯片业界的前列。既实现高端去抖时钟芯片的国产化,也实现了65fs rms抖动性能,同时还具有全面的数字锁相环功能,专为满足112Gbps PAM4 Serdes和5G无线单元而设计。

基于6G场景对时钟信号的高要求,赛思自研出一款时钟输出抖动优于200飞秒的高性能SOC时钟芯片

新华社最新消息,我国率先搭建了国际首个通信与智能融合的6G外场试验网,实现了6G主要场景下通信性能的全面提升。基于6G场景对时钟信号的高要求,赛思设计了一种开环结构的小数分频锁相环量化噪声校准技术,并自研了高性能SOC时钟芯片产品。

【产品】抖动率低至0.3ps的去抖时钟芯片Si5326在光模块中的应用

去抖是光模块接收中极其重要的设计之一。Silicon labs的去抖时钟芯片Si5326采用DSPLL专利技术,输出频率抖动最小可以达到0.3ps,因此常被用于光模块接收器当中用来做去抖设计。

【经验】Silicon Labs时钟芯片Si5332更改时钟输出频率的方法

Silicon Labs推出的Si5332任意频率的时钟发生器提供最高级别的集成,实现在 10/25/100G 数据中心、通信和工业应用程序中的完整时钟树整合。该芯片输出频率范围为5~ 333.33 MHz,具有 175fs 典型值的抖动性能,根据封装不同有 6路、8路、12路-时钟输出。它既可以工厂预先编程,也可以通过I2C接口,进行系统内编程。

大普技术凭借其5G基站高稳时钟,荣获“国家级制造业单项冠军企业”

广东省工信厅公布了国家第八批制造业单项冠军企业名单,大普技术凭借其在5G基站高稳时钟领域的创新技术、先进制造和工艺、卓越品质以及市场占有率全球领先,跻身“英雄榜”,从专精特新“小巨人”企业跃升为“国家级制造业单项冠军企业”。

【产品】更适合IEEE 1588设计的超低抖动时钟芯片SI5388/SI5389

Silicon Labs在充分调研了各大设备商的IEEE 1588产品设备后,实时发布了另外一款支持最新IEEE 1588协议的时钟芯片SI5388/SI5389,并且在全球主流的通信设备厂家配合Xilinx、Intel等平台进行了完整的同步测试。

【选型】三点关键因素决定5G基站时钟选择SI5386A-E-GM还是LMK04828

Silicon Labs SI5386A-E-GM集成DSPLL核心技术的JESD204B去抖时钟芯片,广泛用于5G基站设备中。SI5386A-E-GM和LMK04828都是目前比较主流的无线时钟发生器,但是相对于SI5386A-E-GM来说,LMK04828部分性能、应用特点是无法媲美的。

以5G基站为“主战场”,时钟产品助力数字化生活

通信是万物的基础,而时钟则是通信的基石。作为全球领先的全等级高稳时钟、多品种时钟芯片、射频器件及整体时钟产品解决方案的供应商,大普技术的时钟产品已广泛应用于通信设备、卫星导航定位、汽车电子等领域。在这个竞争激烈的市场中,大普技术以其深厚的技术积累和卓越的产品质量,成功地脱颖而出。

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

【经验】Silicon Labs时钟芯片Si5332写入配置寄存后无频率输出解决方法

Si5332是Silicon Labs公司推出的任意频率的时钟发生器,被广泛应用于消费电子、电信传输网、基站、数据中心等。该芯片输出频率范围为5~333.33 MHz,具有175fs典型值的抖动性能,同时该芯片具有任意频点输出、可内置多组频率计划等特点。在应用中,Si5332在写入配置寄存器后,没有频率输出,该如何解决呢?本文将详细讲解。

赛思携携高精度时钟芯片、5G高精度时频同步设备等闪耀慕尼黑华南电子展,创新科技引领未来!

慕尼黑华南电子展于2023年10月30日至11月1日在深圳国际会展中心(宝安新馆)举行,赛思作为参展商,在现场展示了自主研发生产的授时产品,深获关注。

电子商城

现货市场

服务

可支持TI AM335x/AM5718 和NXP iMX6/iMX8芯片定制核心板和计算单板;支持NXP iMX6核心模组X / F / H系列、TI AM335x核心模组X / N / H系列,与兼容的底板组合定制单板计算机。

最小起订量: 1pcs 提交需求>

世强深圳实验室提供Robei EDA软件免费使用服务,与VCS、NC-Verilog、Modelsim等EDA工具无缝衔接,将IC设计高度抽象化,并精简到三个基本元素:模块、引脚、连接线,自动生成代码。点击预约,支持到场/视频直播使用,资深专家全程指导。

实验室地址: 深圳 提交需求>

查看全部1条回复