【经验】一文了解Latch-up及其保护措施

SCR结构(PNPN结构)是CMOS工艺的固有结构之一。由于该结构内建正反馈机制,其一旦被触发,很容易发生所谓闩锁效应(latch-up)。而latch-up一旦发生,就很容易导致芯片烧毁。又由于SCR结构是寄生的器件结构,通常也没有SPICE模型支持对其进行仿真验证,电路设计工程师常常会觉得latch-up就如幽灵一般琢磨不透,还时不时出来捣乱一番,防不甚防,甚是让人头疼。因此,latch-up就常常会引起芯片设计工程师甚至系统设计工程师恐慌,也常常对latch-up过度敏感。本文思瑞浦带大家来了解Latch-up及其保护措施。

这篇文章试图通过对SCR结构、latch-up的发生机制进行详细理解,从而揭开其神秘的面纱。然后提供芯片级和系统级的防latch-up的解决方案。从而使得芯片设计工程师和系统设计工程师能对latch-up有个清晰的理解,在电路和版图设计过程采取相应的措施,提高芯片和系统抗latch-up的能力。

一、Latch-up原理

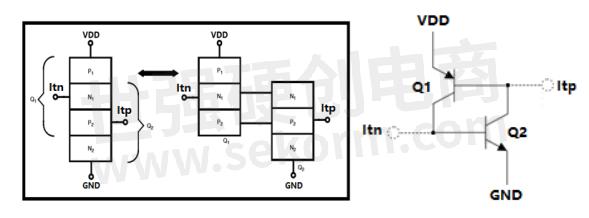

SCR结构,即PNPN四层器件结构。如图一所示,SCR结构由两个bipolar器件(Q1:PNP,Q2:NPN)构成。PNP管的基极同时也是NPN管的集电极,PNP管的集电极也同时是NPN管的基极。如果有触发电流Itn流进Q2的基极并使得Q2进入放大工作区,则由于Q2的集电极电流就是Q1的基极电流,Q2的集电极电流会被Q1进一步放大。被Q2和Q1放大后的电流又作为基极电流流入Q2的基极,然后再进一步放大,如此形成不断放大的正向循环。同样的道理,如果有触发电流Itp从Q1的基极流出并使得Q1工作在放大区,由于Q1的集电极电流就是Q2的基极电流,则Q1的集电极电流会被Q2进一步放大,被Q1和Q2放大后的电流又作为基极电流流入Q1的基极,然后再进一步放大,形成正向循环,就形成所谓的latch-up。一旦latch-up发生,即使撤离触发电流Itn或Itp,latch-up还是会一直持续,以至芯片烧毁。

图一:四层PNPN(SCR)结构及其等效电路图

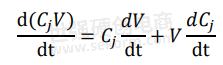

除了基极电流Itn,Itp可能触发CMOS的寄生SCR结构引起latch-up,电源(VDD)或地(GND)的快速变化也可能触发latch-up,这就是通常所说的“dv/dt”效应。图一中N1-P2结处于反偏状态,但是反偏电压的快速变化会引发结电流。结电流的大小见下面的公式。

其中,Cj为N1-P2的结电容。如果结两端反偏电压的变化率足够快,等式右边第一项会占主导,并且流过结的电流会增大,当流过结的电流足够大时,则会触发latch-up。

前面讲述了latch-up的电流触发模式。除了电流可以触发latch-up,超过SCR结构的击穿电压也会触发latch-up。随着SCR结构两端(VDD-GND)的电压升高,SCR结构中的两个bipolar管Q1和Q2的集电极-发射极漏电流也会升高,当漏电流升高足够大时,便使得SCR结构进入latch-up。值得注意的是,无论是连续的还是瞬时的过压脉冲,都可能触发latch-up。

另外,无论电流触发还是过压触发模式,温度的升高,都会使得流经SCR的漏电流增大,因而使SCR结构更容易被触发进入latch-up。

二、CMOS输出的SCR结构及其latch-up触发模式

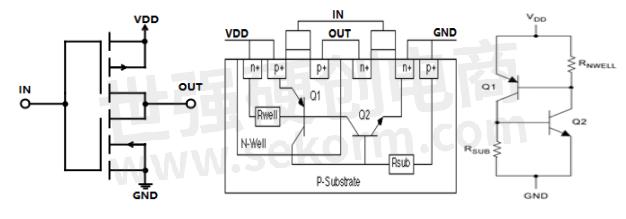

如图二所示,CMOS输出的电路连接及其寄生的SCR结构。PMOS管的Source和Bulk接到电源VDD,NMOS管的Source和Bulk接到地GND,PMOS和NMOS的Drain接在一起作为输出端,Gate接在一起作为输入端。

图二:CMOS输出电路及其寄生的SCR结构

通常,输出电压超出电源或地电压是CMOS输出结构中最常见的latch-up触发模式。假定用Vlatch,Ilatch分别表示触发latch-up的电压、电流条件。Ilatch表示流过输出电路并触发latch-up的最小电流,Vlatch表示超过电源或地并触发latch-up的最小电压,Vlatch也表示超过电源或地并引起流过输出电路的电流达到Ilatch时的电压。如输出电压低于地(GND)达到或超过Vlatch,则会引起寄生NPN(Nwell-Psub-Ndrain)的基极-发射极正向导通从而触发图二中的SCR结构进入latch-up。同样,如果输出电压高于电源(VDD)达到或超过vlatch,则会引起寄生PNP(Pdrain-Nwell-Psub)的发射极-基极正向导通从而触发图二中的SCR结构进入latch-up。

值得一提的是,通常在产品的datasheet中对输入输出管脚有0.3V和10mA的电压电流限制。其中0.3V和10mA是用于量产测试的值而被写进datasheet中的。而实际中,要达到触发latch-up的电压(Vlatch)通常会超过电源或地0.6V~2V,而触发latch-up的电流(Ilatch)从50毫安到几百毫安。

以上讲的都是输出电压高于电源电压或低于地电压,会导致寄生bipolar的基极-发射极正偏,从而触发latch-up。还有另外两种情况尽管不太经常发生,但也得引起注意。一种情况是输出电路本身的电源电压(VDD-GND)过高,如超过绝对最高电压(the absolute maximum rating voltage),则可能引起雪崩击穿而触发latch-up。另一种情况是电源电压中如有非常快速的尖峰脉冲,则如前文所述的“dV/dt”触发SCR结构进入latch-up。

三、芯片级latch-up解决方案

前面讲到电流流过SCR结构就可能触发latch-up,因此器件级或芯片级抑制latch-up发生的方法就是让从SCR结构(见图一P1N1P2N2结构)中P1出来的空穴和从N2出来的电子尽量在N1(PNP的基区)和P2(NPN的基区)区域被复合掉,使得从P1到N2的电流减小。大家只要记住一句话,电子和空穴,其实也是很单纯的家伙,哪里容易去,他们就去哪里,就像他们本来想去看朋友,走到半路看到一个美女在对他们打招呼,于是就很自然的跑到美女那边去了。芯片级latchup所有的解决方法,要么是阻止(加大N+,P+之间的距离,STI,SOI)电子或空穴去看美女,要么找个更漂亮的美女(guard ring)吸引他们过去。总之,就是不要让他们达到P1或N2。

1.加大P1,N2之间的距离,这是最容易想到的办法。电子和空穴也是这样。但是,加大P1,N2之间的距离,必然会导致芯片的集成度降低。

2.隔离(isolation),就是在NMOS和PMOS之间加隔离,比如STI(Shallow Trench Isolation,0.25μm以下的工艺)和场氧隔离(Field Oxide Isolation,0.35μm工艺以上)。

3.深度隔离—SOI(Siliconon Insulator),就是将NMOS和PMOS完全隔离在一个个硅(Si)岛上。这样就完全将电子和空穴隔离开来了。

4.倒阱(retrograded well)工艺,用高能离子注入将杂质打入阱的底部。倒阱不像常规的阱表面浓度最高,阱底部浓度最低,而是相反,所以叫做倒阱,阱底浓度最高。电子空穴到了基极以后,高浓度的深阱可以有效的增加复合。

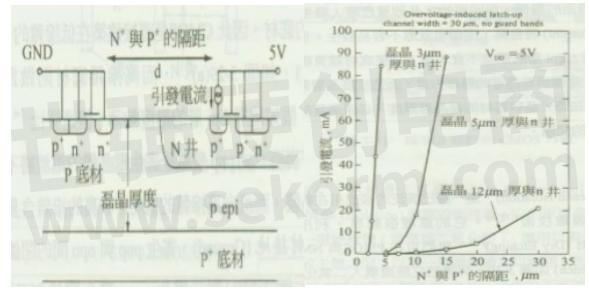

5.Epitaxial(Epi)Wafer,就是在重掺杂衬底(heavy doped substrate)上面,加上一层轻掺杂(lightly doped)外延层作为CMOS制程的衬底。因此CMOS是直接建立在轻掺杂Epi-layer(外延层)上。当这层外延层够薄的时候,pnp的载流子就不想去npn那里了,而是跑到更舒服的重掺杂衬底,因为重掺杂衬底的浓度比外延层的掺杂浓度高多了。如图3所示,很明显,外延层越薄越好。但是也不能太薄,不然重掺杂衬底的离子就扩散到外延层里面,造成离子浓度改变。图3中,3μm的外延层,触发电流(引发latch up的电流)最大,最不容易发生latch up。外延层能有效抑制Latch up,这是采用外延层的主要原因。但是Epi wafer缺点就是:贵!

图三 外延层工艺及对 latch-up 触发电流的影响

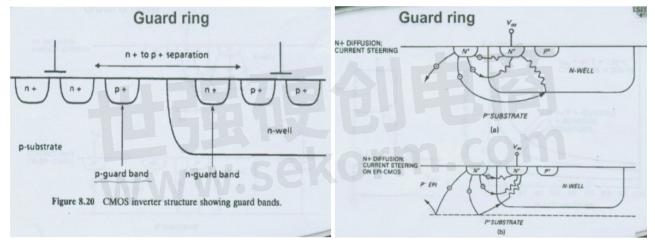

6.Guard Ring,在P1和N2之间加一个guard ring,目的就是使得电子空穴在guard ring这里就被吸收了。如图四。

图四:Guard ring示意图及对N-guard ring对载流子行程的影响

7.Design Rule,这个比较容易理解,就是在画版图的时候,规定P1,N2之间的距离、guard ring的宽度、guard ring离P1和N2的距离等等。

但是,这么多的解决方案,到底用哪一个呢?答案其实很简单,能用的就一起用!但是也要考虑芯片面积,考虑成本哦!

四、系统级latch-up

系统级引起latch-up的主要潜在情况有:

1)系统运行或维护过程中,将PCB板从带电系统中拔下或插入带电系统。

2)系统存在多电源供电,如+/-12V,+5V和地或者虽然电压相同,但由不同电压组供电,如+5V regulated电源和+5V unregulated电源。

3)电路板上各电源使用复杂的电容去耦方法,特别是多电源系统。

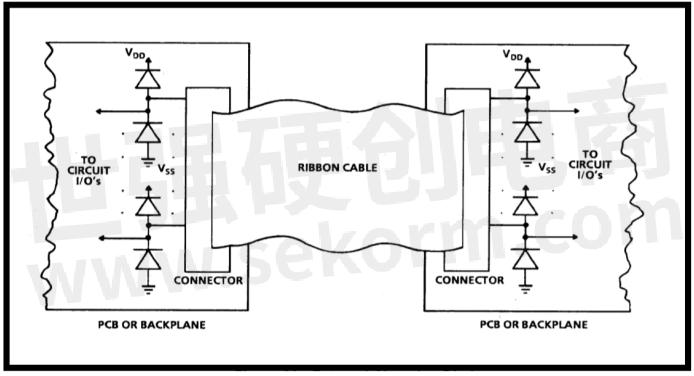

4)不同PCB板上的集成芯片通过背板(backplane)或带状电缆(ribbon cable)连接。

5)一颗芯片驱动大电容值负载,例如较长的数据线或地址总线。

6)高速且较长的数据或地址总线引入的电感,导致过高电压(over voltage)。

7)系统带有终端用户容易接触到的I/O端口。

8)数字IC和模拟IC处于同一系统中。

下面将针对以上八种情况一一分析每一种情况下可能引发latch-up的原因,并提出相应的解决方案。当系统设计工程师遇到问题时能处变不惊,不致束手无策。

五、带电插拔PCB板

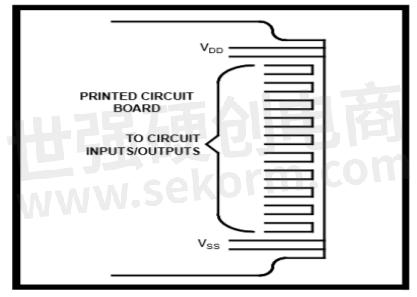

如果不做预先的处理,带电插拔PCB板可能通过几种方式触发latch-up。其中一种潜在的危害是可能发生输入输出(I/O)管脚先于电源管脚与带电母板接触。系统中与之连接的电路会对该PCB板的I/O管脚先于电源管脚上电。尽管上电时间差很短,只要I/O管脚的电压超过电源电压达到Vlatch,就可能触发I/O端寄生的SCR结构进入latch-up。需要注意的是,即使是三态输出管脚(tri-state output),也易于发生latch-up。输出管脚处于高阻态,只能说明输出管脚到电源或地是高阻态,但是,只要输出管脚的电压超过电源电压或者低于地电压达到Vlatch,就可能引发latch-up。一种解决的方案是将电源和地分别置于PCB板的两边,这样可以保证电源和地总是先于I/O插入母板上电。如图五所示。

图五:将电源、地至于插线板两端避免I/O先于电源、地上电

六、多电源系统板

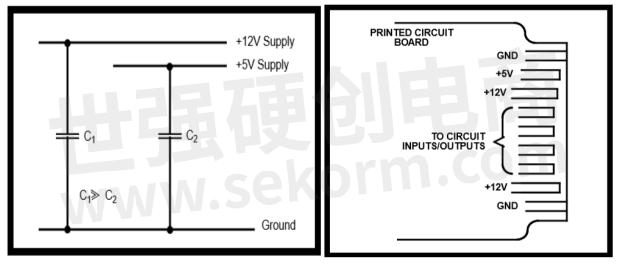

带电插拔的另一种情况是多电源系统板,其每个电源的去耦电容值相差较大。如图六所示。假定+12V电源、地线、+5V电源与母板先后连接,且C1>>C2,则当地线连接后,5V电源线上的电压可能会被抬高(pump)到12V,如果该电压超过了连接到5V电源线上各器件的雪崩击穿电压,则可能引发latch-up。多电源系统的各电源相差越大,这个问题就显得越明显,因为连接在较低电源的器件发生过压的可能性就越高。一个典型的例子是电话交换系统,其中包含了-48V、+5V及其他电源电压。

图六:多电源,且去耦电容相差很大 图七:多电源在插线板上的分布顺序

这个问题也可以通过优化PCB板设计加以解决。最安全的解决方案是让较低电压的电源先与母板连接上电。如图七所示,针对+5V,+12V,-12V及地线,连接顺序应依次为地线、+5V,然后+12V和-12V同时连接上电。倒序连接可以保证各电源不会由于去耦电容引发过压(over voltage)。记住,地线应当总是首先与母板连接的管脚,保证正电源不会被拉负,负电源不会被拉正。

另外,在多电源系统板上,应尽可能对各电源管脚用相同电容值的去耦电容。

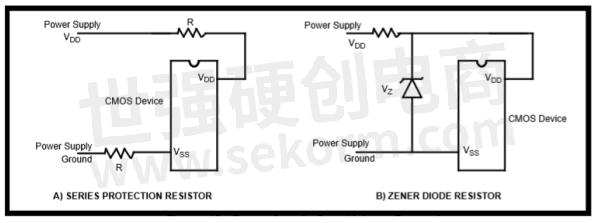

如果所有这些预防措施都已采取,系统仍然有过压产生,则有必要采取限流措施。最简单的措施就是在电源(Vdd或Vss)上串接电阻。电阻阻值可以由下面公式计算。

R=(Vsupply−Vddmax)/Iddmax

其中,Vsupply就是系统上出现的最高过压,Vddmax是电源上能承受的最高电压,Iddmax是在Vddmax时的电流。

图八 在电源上串限流电阻或加钳位二极管

如果限流电阻太大,影响到输出电路的驱动能力、速度或噪声(output drive,speed or noise immunity),则如图八所示,可以采用齐纳二极管(zener diode)连接在Vdd和Vss之间,以阻止过压发生。尽管采用了zener diode,限流电阻可能还是需要,以保护齐纳二极管本身。但是这时候所加电阻可能就不需要太大。

对于带电插拔PCB板,还有一种风险是去耦电容太小,插拔PCB板可能引起电源电压瞬变脉冲,如前所述,快速的dv/dt可能引发latch-up。解决办法就是加足够大的去耦电容。但是也得考虑与PCB板上其他电源上的去耦电容匹配。避免前文所述的去耦电容引发的问题。

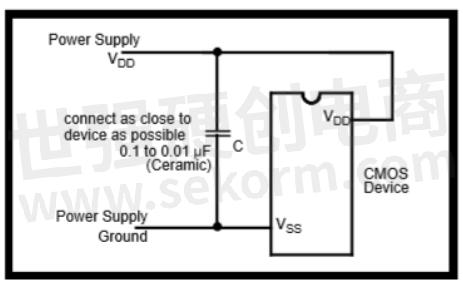

在电源线上除了带电插拔引起瞬变脉冲,还有很多其他因素引发瞬变脉冲,如高速switching、大电流IC(如ECL,Schottky TLL)驱动重负载(heavy current loads)。另外,电感负载产生的反电势(back EMF)也可能产生严重的电压脉冲。这时,如图九所示,可用高频电容,如0.01~0.1μF的陶瓷电容(ceramic capacitor)靠近IC电源连接。同时最好加flyback diode以钳位反电势浪涌的幅度。

图九:在电源上加高频去耦电容滤除电源毛刺

七、多电源及其去耦电路

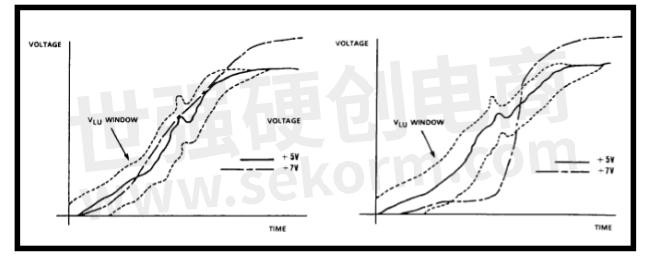

如前所述,多电源系统,必须注意各电源的上电、掉电顺序。地线需要首先连接上电,然后从电压较低的电源开始上电。目的就是从PCB板的设计阶段就考虑防止在输入输出管脚出现过压情况。例如,一个以+5V供电的器件,与其输出连接的是一个以+7V为电源的器件,在稳定条件下,从5V电源域输出的电压定会低于7V电源域。但是,在上电过程中,5V电源域可能会高于7V电源域,如图十所示,连接到5V电源域器件的输出电压可能短时内超过7V电源域的电源电压,从而引起连接在7V电源的器件发生latch-up。即使电源电压相同,如果分别由不同的电源供电,也会出现相似情形。在上电过程中,即使是非常短暂的过压脉冲,也可能引发latch-up问题。

图十:多电源上电过程中latch-up的风险

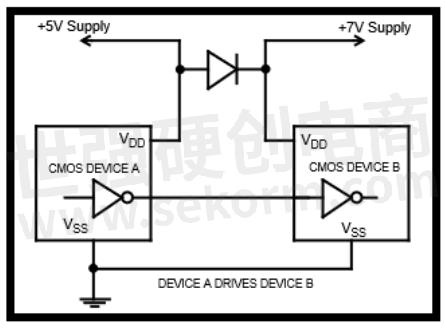

如图十一,在两组电源之间加二极管,可以保证在上电过程中,当较高电压的电源还未建立之前,较高电压的电源只会比较低电压的电源相差一个二极管的电压。如果两组电源电压相等,则在他们之间用背靠背的二极管(back-to-back diodes)相连。

图十一:多电源之间的二极管耦合电路

八、不同PCB板之间的连接

在同一系统中,不同PCB板之间的驱动连接的考虑,如前述几部分——带电插拔PCB板和多电源及其去耦电路——I/O管脚的潜在风险是当电源还未上电,I/O电路已经被连接到带电母板或其他PCB板,而引发latch-up。其解决方案是将地线、电源按电压从低到高依次靠近PCB板边沿,输入输出管脚放PCB中间。但是,对不同PCB板之间,即使是每一块PCB板只有一组电源,也要小心考虑各PCB板上电源的去耦电容。如果一块PCB板的电容较大,另一块PCB板的去耦电容较小,则可能导致上电速度不同。去耦电容小的,上电速度较快,可能导致其输出电压高于下一块PCB板的电源电压,从而如在多电源及其去耦电路中介绍的那样,引发latch-up。

因此,无论什么时候,整个系统上各PCB板上的去耦电容都尽可能用同样大小的电容值。如果可能,在上电和掉电过程中,所有输出管脚应当保持高阻态,这样即使各PCB板之间存在电压差,也没有输出电流触发latch-up了。

另外,也可以在可能出现过压(over-voltage)的输入输出管脚上串接限流电阻。电阻的大小可以由下面的公式计算。

R=(Vdiff-0.3V)/10mA

其中,Vdiff是两组电源之间可能出现的最大电压差。当然,增加限流电阻带来的负面影响如前所述为:电流驱动能力、速度、抗噪能力等。前面提到,通常在产品的datasheet中对输入输出管脚有0.3V和10mA的电流限制,其中0.3V和10mA是用于量产测试的值而被写进datasheet中的。而实际中,要达到触发latch-up的电压(Vlatch)通常会超过电源或地0.6V~2V,而触发latch-up的电流(Ilatch)从50毫安到几百毫安。

九、大电容值负载

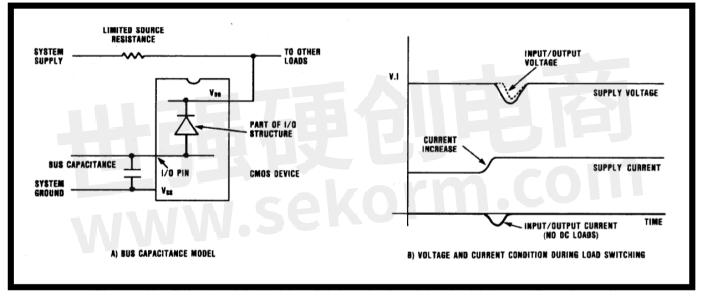

长的地址或数据总线能带来非常大的寄生电容。一颗芯片驱动长的地址或数据总线可能会遭遇到过压条件,从而触发

latch-up。特别是在同一块PCB板上,当大的电流负载同时切换(switch)的时候,例如一组LED在做灯泡测试(lamp test)时,就可能发生过压。电源电流的变化会导致电源管脚上的局部电压降,这是因为大电流流过电源线上寄生的连线电阻以及连接器的接触电阻从而产生电压降,与此同时,线上电容又将I/O端的电压保持住不使其改变,如图十二所示。如果电源和I/O端的电压差足够大,则总线电容会经由I/O结构放电,该放电电流可能达到几十毫安,因此可能触发latch-up。

图十二:电源线电阻和大电容负载引起I/O和电源间电压差

因此,在PCB板设计之初,就应当考虑尽量减少电源线上的连线电阻和总线上的寄生电容。如尽量宽的电源走线和尽量低的连接器的接触电阻。地址和数据总线应当尽可能短,同时它们之间的走线距离尽可能离得远。采取这些措施后,如果还会发生 latch-up,则可在电源之间加上去耦电容以减小电源上的电压波动。电容值的大小取决于局部电流的大小和电源线上的连线电阻。通常10μF的电容就可以。

十、电感负载

带状电缆(Ribbon Cable)作为长距离总线,除了需要注意前一节提到的大电容负载问题,还会引入较强的电感。足够大的电容电感就形成了二阶电路,当输出较快的信号时,可能引起振荡。如图十三所示,如果振荡幅度够大,则输出信号的电压可能超过电源电压,如果达到Vlatch,则会引发latch-up。

图十三:电容电感引起输出信号叠加振幅较大的振荡

解决的办法是在带状电缆的两端加上适当电阻。但是,加入的电阻则引起额外的功耗。另一种方案如图十四所示,在I/O端加入保护二极管,二极管可以钳位过压脉冲。如果加了普通二极管还是会出latch-up的问题,则可能需要用肖特基二极管,以保证足够快和足够低的钳位,不至于让I/O电压超过电源电压达到Vlatch,从而避免触发I/O端口电路的latchup。

图十四:I/O端加二极管以钳位I/O与电源之间的电压差

十一、容易接触的I/O端口

终端用户容易接触到的端口,很容易受到静电或用户非正常上电而导致latch-up,如果I/O电压先于电源上电,这时,I/O端口电压会高于电源电压,则I/O端口的电路很可能触发latch-up。解决办法之一就是在端口电路上串接限流电阻。但是,如前文所述,该限流电阻则会影响该端口的速度和抗噪等性能。

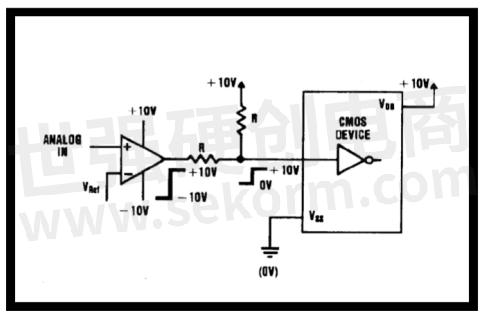

十二、数字IC和模拟IC同处同一系统板

在同一个系统板中,同时存在模拟和数字电源管脚,特别是不同电源电压,则有潜在的过压风险,过压则可能触发latchup。例如,一个模拟比较器,其电源电压为+/-10V,驱动一个电源为+10V的数字电路,当比较器的输出为低时,即-10V,则其电位远低于数字电路的最低电位VSS(0V)。如果比较器的驱动电流足够大,则可能触发数字电路中I/O端口的latchup。当然,可以在数字输入端加入限流电阻限制latch-up的触发。但是,一种更加推荐的方案是在数字输入端采用电阻分压,如图十五所示,当比较器的输出为低时,电阻分压器上有20V(+10V~-10V)的电压,则数字电路的输入电压为分压电阻上一半的电压,即0V。当比较器的输出电压为高时,则没有电流流过分压电阻,因此,数字电路的输入为VDD。CMOS输入的输入阻抗一般都非常高,因此,可以用非常大的电阻作为电阻分压,以减小功耗。

图十五:模拟IC和数字IC之间的连接

最后,作者希望通过这篇文章,让芯片设计工程师、芯片版图设计工程师、系统设计工程师、以及应用工程师对SCR结构、latch-up的发生机制有所理解,当遇到latch-up的问题时能处变不惊,不致束手无策。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由奶爸工程师转载自思瑞浦,原文标题为:Latch-up及其保护措施,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关研发服务和供应服务

相关推荐

【经验】使用肖特基二极管设计输入保护电路,防止ADC击穿现象

某客户设计一款电子秤项目,采用3PEAK 3PA9280作为输入采样ADC,单电源供电,在应用中放大器采用±15 V供电,而ADC输入为0至5V。高压电轨用于接受±10 V输入,同时给ADC前端信号调理/驱动级供电。放大器驱动电源电压偶尔会出现不稳定情况,因超过最大额定值而损坏ADC,本文主要帮助客户介绍一种输入保护电路。

【经验】以电流感应放大器TP199为例介绍电流检测设计要点

思瑞浦的TP199 是专用的电流感应放大器。配合检测电阻实现高精度电流检测。被广泛的应用于电子烟,BMS,电源,充电器,工业设备等产品。本文试以此产品为例介绍电流检测设计要点。

【经验】思瑞浦RS-232收发器TP3232N应用指南

思瑞浦推出的RS-232收发器系列产品具有低功耗、高数据速率、高可靠性等优点,内部包含两个发射器和两个接收器,完全符RS-232工业标准。本文将就思瑞浦RS-232收发器TP3232N进行应用指南分享。

零漂移双向电流感测放大器TPA191用于电控聚焦显微镜相机,宽共模电压-0.3 V至+36 V

随着技术的发展,各种系统逐渐往细小、精密的方向发展,本文针对电控聚焦显微镜相机系统中电机状态检测,常规编码器体积过大,推荐使用思瑞浦的电流检测芯片TPA191A2-SC6R,通过连接在驱动芯片的检流电阻,对电流回路进行采样,后端输出通过ADC转换后传到MCU。TPA191系列,20 V/V~200 V/V的五档增益选择,满足不同使用情况;REF引脚接地和二分之一Vs分别可以用于检测单向电和双向电。

TPA1286高电压、精密、零漂移仪表放大器

描述- TPA1286是一款高电压、精密零漂移仪表放大器,具有出色的直流规格和低噪声特性。该产品适用于多种单电源电压,提供宽输入范围和轨到轨输出,以充分利用电源轨。它采用单个外部电阻设置增益(范围为1至1000),并具备优异的共模抑制比和高精度。

型号- TPA1286U-SO1R,TPA1286-VS1R,TPA1286-SO1R,TPA1286U-VS1R,TPA1286U,TPA1286,TPA1286U-DF7R

Buck变换器的发展

描述- 本文主要介绍了降压转换器(Buck Converter)的发展历程、工作原理、控制方案以及应用。从线性电源到开关电源,再到同步整流技术,降压转换器在电子设备中的重要性日益凸显。文章详细阐述了电压模式控制和电流模式控制两种控制方案,并介绍了COT(恒定导通时间)控制架构的优势。此外,文章还讨论了陶瓷电容在降压转换器中的应用以及3PEAK公司开发的TPP2020降压转换器的性能特点。

TP181零漂移、双向电流检测放大器

描述- 该资料介绍了TP181系列零漂移双向电流检测放大器。这些放大器能够在-0.3V至36V的共模电压下感应电阻上的压降,不受供电电压的影响。提供三种固定增益选项:50V/V、100V/V和200V/V。低偏移量架构使得在分流器上的最大压降可低至10mV满量程。TP181器件可在单+2.7V至30V电源下工作,典型功耗为120uA。所有版本均指定从-40°C到+125°C,并采用SC70-6封装。

型号- TP181A2,TP181A1-CR,TP181 FAMILY,TP181 SERIES,TP181A1,TP181A2-CR,TP181A3-CR,TP181,TP181A3

【应用】基于电源时序控制器TPK1032的纯硬件搭建电路,实现9路电源上下电顺序可控

思瑞浦TPK1032是一款简单易使用的电源时序控制器,提供多通道电源的上电和断电时序控制。TPK1032为开漏输出,建议上拉电阻选取100K。其所有通道都可以上拉到任何等于或低于VCC的电压。VCC范围为2.5V~5.5V。

思瑞浦LDO产品有哪些电压输出?

LDO有可调电压输出版本和固定电压输出版本。可调输出电压版本可以通过板外分压电阻来设置输出电压;固定电压输出版本一般会覆盖5V、3.3V、1.8V等常见电压点。

TPL9032系列300 mA高PSRR、超低噪声LDO

描述- 该资料介绍了TPL9032系列线性稳压器(LDO),这是一款高PSRR、超低噪声且具有低 dropout 特性的产品。该系列产品支持从0.9V到5V的固定输出电压范围,并能在1μF或更大容值的陶瓷输出电容器下稳定工作。TPL9032系列具备87.9dB的高PSRR和8.6μVRMS的超低噪声,适用于对电源噪声敏感的应用,如高性能模拟设备和高清成像设备。

型号- TPL9032 SERIES,TPL903230-S5TR,TPL903228-DF1R,TPL903225-DF1R,TPL903236-S5TR,TPL903231-WS1R,TPL903225-S5TR,TPL903233-DF1R,TPL903228-S5TR,TPL9032285-WS1R,TPL903230-DF1R,TPL903233-S5TR,TPL90321875-WS1R,TPL9032XX-WS1R,TPL903231-DF1R,TPL903229-DF1R,TPL9032XX-S5TR-S,TPL9032,TPL903245-S5TR,TPL903218-DF1R,TPL903229-S5TR,TPL903212-S5TR,TPL903218-S5TR,TPL9032XX-DF1R,TPL903215-S5TR,TPL903212-DF1R,TPL903225-WS1R,TPL903233-WS1R,TPL903218-WS1R

【应用】思瑞浦高共模差动放大器TPA9151助力无刷直流电机实现精确电流检测,增益误差最大为0.03%

常见的电机电流检测可采用霍尔电流传感器、电流互感器和采样电阻加运放的方法,而考虑到采用霍尔检测的方案会导致电磁干扰,所以此处使用采样电阻配合运放的方式进行,运算放大器采用的是思瑞浦TPA9151-SO1R进行无刷直流电机的三相检测。

TPTMP75数字输出温度传感器,具有I²C和SMBus接口

描述- TPTMP75是一款数字输出温度传感器,适用于替换NTC和PTC热敏电阻。该设备具有±1°C的典型精度,无需校准或外部信号调理。它包含片上12位模数转换器(ADC),提供高达0.0625°C的分辨率。TPTMP75具有SMBus、两线制和I2C接口兼容性,适用于各种通信、计算机、消费、环境、工业和仪表应用。

型号- TPTMP75-SO1R,TPTMP75,TPTMP75-VS1R

【产品】最大输出电流可达3A的思瑞浦LDO芯片TPL930,输出电压噪声6μVRMS

思瑞浦TPL930 系列LDO芯片是 3A 大电流、6μVRMS 低噪声、高 PSRR、高精度的线性稳压器,具有典型值145mV的超低压差电压。TPL930 系列产品支持 0.8V 至 3.95V 的固定输出电压类型和带外部反馈分压电阻的2.8~5.2V可调输出电压类型。

TPR860x匹配电阻网络

描述- TPR860x是一款匹配电阻网络,由四个匹配电阻组成,具有优异的匹配规格,适用于各种需要匹配电阻的应用。该产品在-40°C至125°C的温度范围内表现出色,匹配精度高,适用于仪表、工业控制、电压参考等领域。

型号- TPR8601A-EV1R,TPR8600-EV1R,TPR8603-EV1R,TPR860X-EV1R,TPR8601-EV1R,TPR8600-EV1R-S,TPR8601-EV1R-S,TPR8601A-EV1R-S,TPR8602A-EV1R,TPR860X,TPR8602-EV1R,TPR8602-EV1R-S,TPR860XA,TPR8600,TPR8601,TPR8602,TPR8602A,TPR8603,TPR8601A

TPP36208x 36 V输入、2 A同步降压稳压器

描述- 该资料介绍了TPP36208x系列同步降压转换器,这是一款简单易用的2A输出电流同步降压开关模式转换器。它集成了低导通电阻功率晶体管,具有内部软启动、补偿和保护功能。该系列产品提供了一种紧凑的解决方案,能够在广泛的输入电压范围内实现高达2A的连续输出电流,并具有良好的负载和线路调节性能。

型号- TPP362081-T6TR,TPP362084-T6TR,TPP362080-T6TR,TPP36208X,TPP362083,TPP36208X SERIES,TPP362084,TPP362085,TPP362080,TPP362082-T6TR,TPP362081,TPP362082,TPP362085-T6TR,TPP362083-T6TR

电子商城

现货市场

服务

整体外形尺寸小至0.6*0.3*0.3mm (DFN0603),工作电压范围覆盖2.5V~36V,电容值低至0.2pF,浪涌能力最高可达240安培,静电等级可达空气放电、接触放电±30KV。提供免费浪涌测试仪、静电测试仪测试。

提交需求>

可定制LAMP LED、 CHIP LED、 PLCC LED、 汽车用车规级LED、COB LED的尺寸/电压/电流等参数,电压1.5-37V,电流5-150mA,波长470-940nm。

最小起订量: 30000 提交需求>

登录 | 立即注册

提交评论