【应用】板卡处理器PCIe 2.0时钟buffer选用奥拉电子Au5411,可同时提供10路差分输出

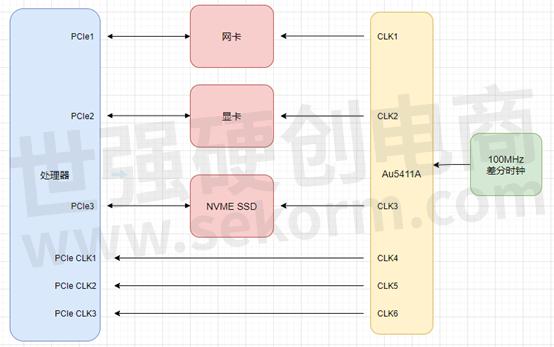

板卡处理器的外部连接了网卡、显卡和SSD,这些设备都通过PCIe 2.0总线进行连接,网卡用于实现以太网通信、显卡用来显示图形界面、而SSD则用于存放操作系统。因为处理器本身不能提供PCIe时钟,需要由外部器件来提供100MHz的差分时钟信号,这里选用了奥拉电子的Au5411A作为PCIe时钟芯片,提供多路100MHz差分时钟给处理器和PCIe外设使用。本文介绍了时钟缓冲器Au5411A的设计和使用方法。板卡主要功能框图如下所示:

图 1 板卡主要功能框图

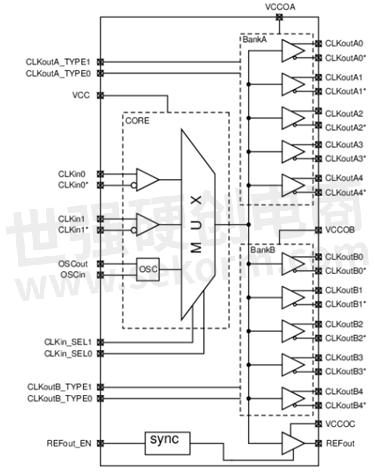

Au5411A是奥拉电子公司的时钟缓冲芯片。最多支持10路差分时钟输出,最高工作频率为2.1GHz,可用于高频时钟应用。Au5411A主要性能特点包括:工作电压范围1.8-3.3V,具有10路输出通道,工作频率范围从DC到2100MHz,支持LVPECL、LVDS、HCSL输入和输入时钟规范,采用QFN48封装等。Au5411A的功能框图如下所示:

图 2 Au5411A功能框图

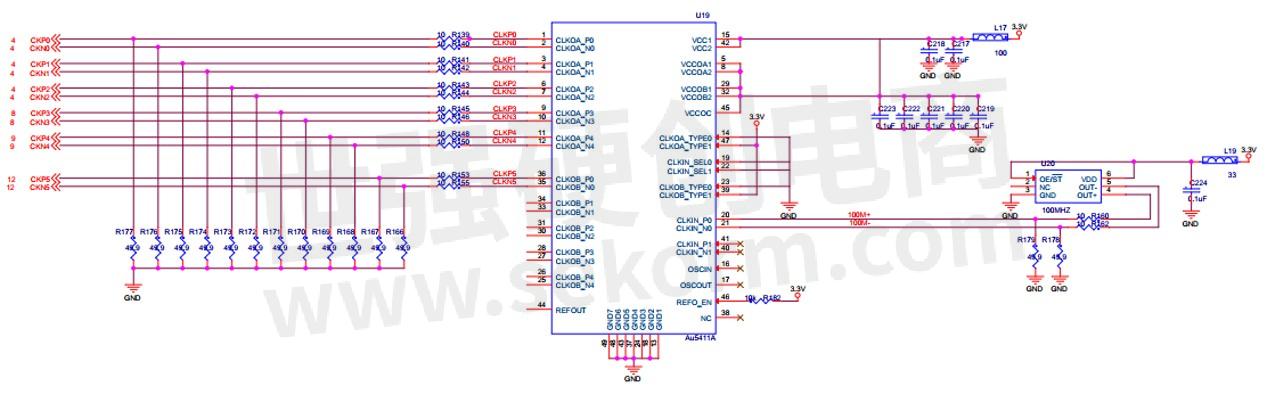

Au5411A原理图设计如下图所示:

图 3 Au5411A原理图

原理图右边为Au5411A的输入时钟,Au5411A共有两组时钟输入,可以从20、21pin输入,也可以从40、41pin,输入信号通过SEL0和SEL1信号控制,这里SEL0和SEL1都接地,所以时钟信号从20、21pin输入。输入信号可以是LVDS、HCSL和LVPECL中的一种,我们采用HCSL类型输入。图中左边为Au5411A的10组输出,其中3组提供给处理器、1组提供给PCIe网卡、1组提供给显卡、另外1组提供给NVME的SSD,总共使用了6组。Au5411A输出时钟类型也支持LVDS、HCSL和LVPECL中的一种,具体采用哪种类型,需要根据接受时钟的芯片来决定,这里因为是用作PCIe接口的时钟,一般采用HCSL类型输出,输出类型由TYPE0和TYPE1引脚进行配置(Au5411A的输出分为A,B两个bank,有两组输出配置引脚,都需要进行配置),这里配置为10,即输出为HCSL类型。HCSL时钟输出需要加50欧姆的下拉电阻,这里选用49.9欧姆的高精度电阻。另外Au5411A的VCCO电源支持3.3V、2.5V和1.8V,需要根据负载情况进行选择,因为时钟频率很高,注意电源引脚需要加适当的滤波电路,确保芯片工作正常。

Au5411A PCB图

Au5411A的PCB设计图如下所示。图中右边为100MHz差分晶振,左边为Au5411A。

图4 Au5411A PCB图

差分超低抖动缓冲器Au5411A的PCB设计需要注意把相关的器件都尽量靠近Au5411A放置,特别是电源的滤波电路,如果正面走线太远,建议把滤波电路放在Au5411A背面靠近引脚的地方,上图的滤波电容都放在PCB背面以靠近Au5411A的引脚。此外不论是输入的100MHz差分时钟,还是扇出的10组100MHz差分时钟,都需要按照差分信号布线规则紧靠一起走线,并且需要做等长处理,保证达到最好的抗干扰效果。

结论

Au5411A是一颗国产的高频差分时钟缓冲芯片,可以提供最多10组输出和最高2.1GHz的时钟频率,可以广泛用于为PCIe、SATA、USB以及SRIO等接口提供可靠的差分时钟。经过我们实际测试,Au5411A完全可以满足PCIe接口时钟的要求。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由深蓝的鱼提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【应用】国产奥拉半导体Au5426时钟缓冲器用于5G通信小基站,支持4差分输出,具有超低抖动性能

对于PCI-e设备要求数量不多的5G通信小基站,时钟缓冲器推荐国产奥拉半导体的Au5426时钟缓冲器,4差分输出和1 LVCMOS输出超低抖动的优秀性能,适用于5G小基站信号处理板的PCI-e时钟分配。

【应用】抖动衰减和时钟合成器AU5315用于高清接口矩阵时钟信号分配,具有4输入到10输出频率转换选项

大量视频数据的处理,需要高宽带的FPGA或处理器,对系统的时钟信号也有更高的需求。针对高要求高标准的时钟信号解决需求,国产奥拉半导体推出了基于可编程四分频转换的抖动衰减和时钟合成器AU5315,适用于高清接口矩阵时钟信号分配。

【应用】国产10路输出的抖动衰减时钟合成器AU5315在交换机数据转发系统的应用,支持频率范围广泛

据交换系统中应用最多的就是Serdes这种串并转换协议,随之而来的就是CDR中时钟恢复的问题,为了避免影响到我们恢复的时钟质量,需要一颗良好的低抖动特性的去抖时钟芯片,奥拉的AU5315就是数据交换板中理想的时钟芯片选择。

【产品】3:1输入时钟选择的时钟驱动器AU5411,可支持10路2.1GHz的低抖动时钟输出

奥拉半导体是一家跨国无晶圆厂半导体公司,专注于高端模拟和混合信号集成电路的解决方案。其推出的时钟驱动器AU5411支持10路2.1GHz的低抖动时钟输出,主要用于低抖动、高频时钟/数据分配和电平转换用途,该缓冲器可以选择从主时钟、次时钟或者晶振输入。

【选型】支持8-50MHz晶体输入的Au5411A-QMR时钟buffer用于通信管理机,可简化电路节约PCB板空间

电源、时钟、复位时硬件电路三大核心电路,具有举足轻重的地位,对于产品的正常工作非常重要,本文主要介绍奥拉电子时钟buffer Au5411A-QMR在一款通信管理机中的应用。

【选型】奥拉时钟驱动器AU5426A-QMR用于光端机,支持4路差分输出和1路单端输出

某用户在研制光端机时需求时钟buffer,要求低抖动,最好是国产的,推荐奥拉的时钟驱动器AU5426,它是一款支持4路差分输出和1路LVCMOS输出的超低抖动时钟和扇出缓冲器,该缓冲器可以选择来自主时钟、次时钟或晶振的时钟输入。

AU5411 – 10 OUTPUT, DIFFERENTIAL, ULTRA LOW JITTER BUFFER

型号- AU5411,AU5411A-QMR,AU5411A-EVB,AU5411A-QMT

奥拉半导体产品选型表

供电电压频率(≤250MHz),相位噪声(<50fs),输入/输出,封装类型,输出频率范围(0.5 Hz-2.94912 GHz),输出电流(A),频率,输出精度,静态电流,噪音,压降,电源抑制比

|

产品型号

|

品类

|

供电电压(MHz)

|

相位噪声(fs)

|

输入/输出

|

封装类型

|

|

AU5424BG-DNR

|

时钟驱动器

|

≤200MHz

|

<50fs 附加抖动

|

1:4 LVCMOS 缓冲器

|

8-DFN

|

选型表 - 奥拉 立即选型

AU5426A: 4 Differential and 1 LVCMOS Output Ultra Low Jitter High Performance Buffer

型号- AU5426A-QMR,AU5426A-EVB,AU5426A

AU5426: 4 Differential and 1 LVCMOS Output Ultra Low Jitter High Performance Buffer

型号- AU5426A-QMR,AU5426,AU5426A-EVB

【经验】奥拉低抖动时钟buffer Au5411同差分时钟格式输出的实现方式

奥拉低抖动时钟buffer Au5411可支持10路差分时钟输出,包括LVPECL, LVDS, HCSL or HIZ 等格式、超低附加抖动55fs RMS,可广泛应用于基站、服务器等场景中。本文将介绍不同差分格式输出的实现方式。

Aura Timing Product Overview

型号- AU5424,AU5325,AU5425,AU5426,AU5327,AU5327BC1-QMR,AU53X7,AU5325BC1-QMR,AU5315,AU5508,AU5317,AU5508 SERIES,AU5315AC0-QMR,AU5328,AU5329,AU5329B-QMR,AU5325BC2-QMR,AU5411A-QMR,AU5327BC2-QMR,AU53X5,AU5410,AU5411,AU5615,AU5424G,AU5617,AU5317AC0-QMR,AU5424A,AU53X7 SERIES,AU5410A-QMR,AU53X5 SERIES

【视频】奥拉包含JA、Buffer、NS和时钟发生器在内的多品类时钟器件,抖动值最小可达80fs

型号- AU5331,AU5411,AU526X,AU5410,AU5325,AU5424,AU524X,AU5415,AU5327,AU5426,AU5417,AU5329,AU5508

电子商城

服务

可定制B-Flon高频同轴电缆的温度-40~105℃、尺寸长度,采用导体规格:AWG28~36,减衰量:1GHz-6GHz/1.4-8.5db/m,阻燃UL:VW-1规格。

最小起订量: 50000m 提交需求>

提供蓝牙BLE芯片协议、蓝牙模块、蓝牙成品测试认证服务;测试内容分Host主机层,Controller控制器层,Profile应用层测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论